ARMv9以及公版CPU有什么重大改进

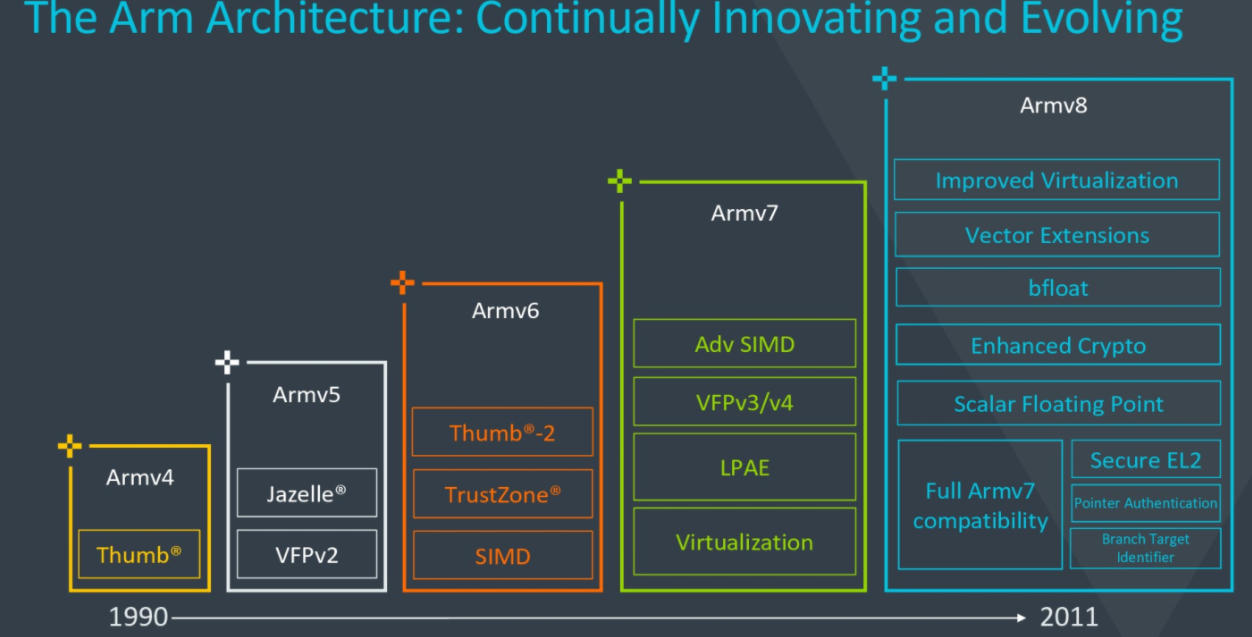

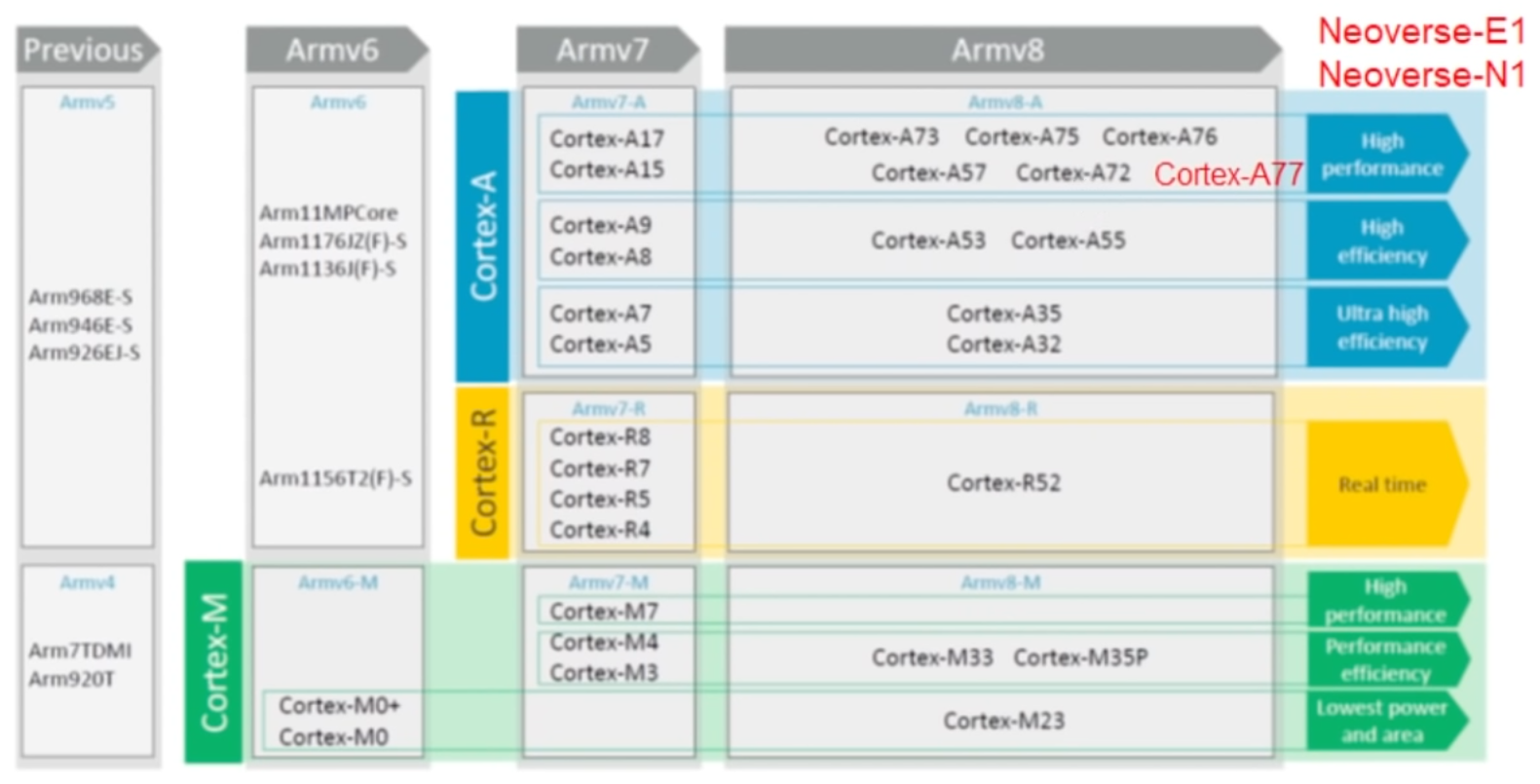

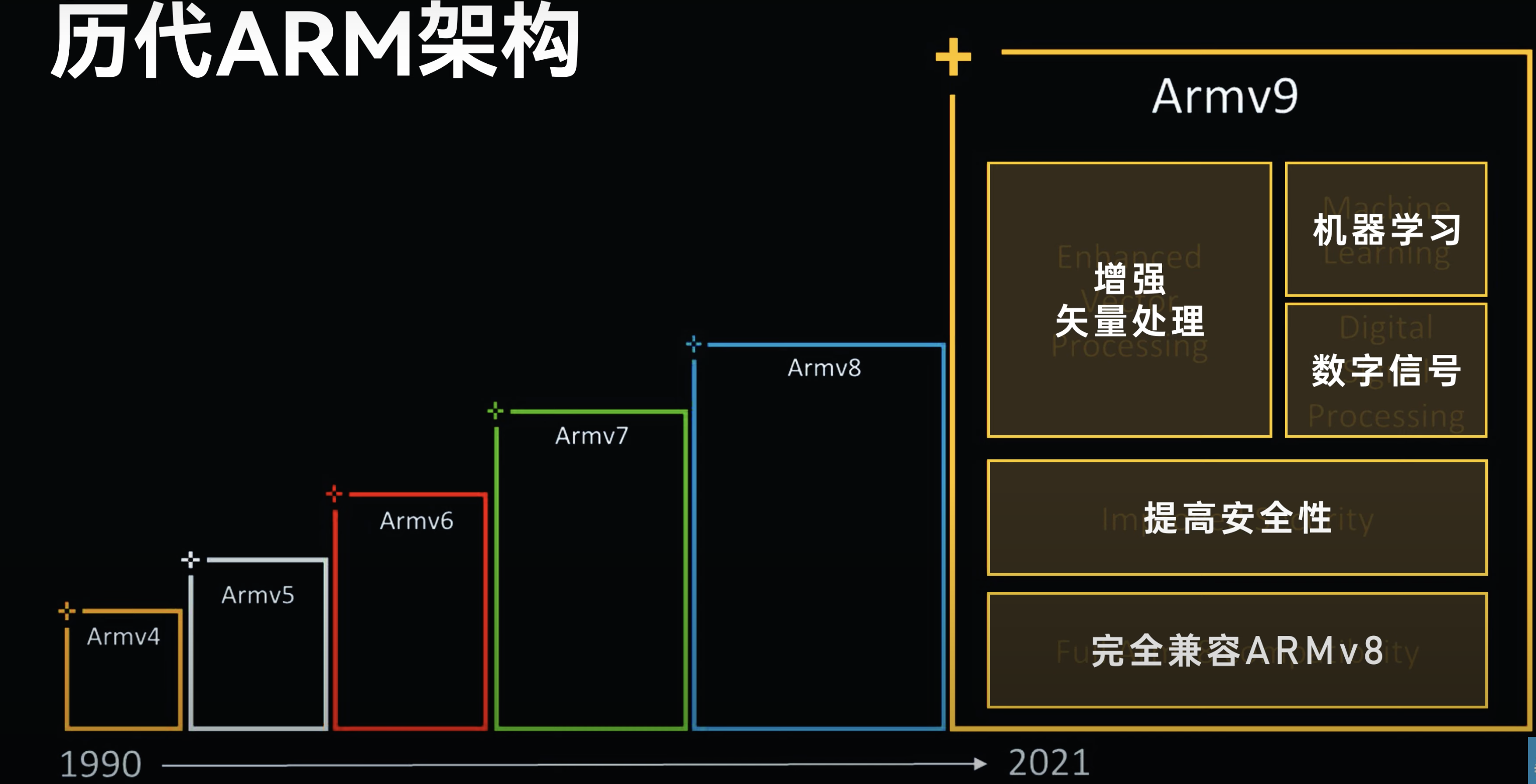

ARM v9 是继v8发布后十年来的一次重要的指令集的升级,我之前写过一篇《ARM 架构家族史》,ARM 从v7架构以后,将CPU分成了三类。如下图:A系列,R系列和M系列,各自针对不同的的领域。

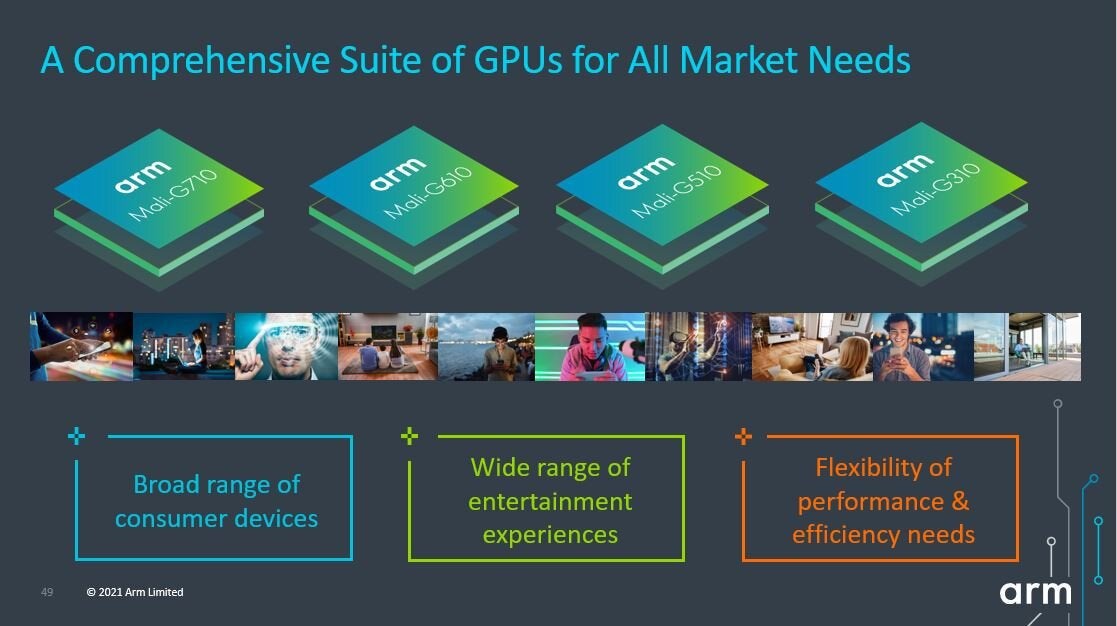

ARM在发布v9架构后,又发布了三款公版 CPU IP 和四款GPU IP。

关于新的GPU IP我会单独写一篇文章来分析。今天我们重点来看一下2021年发布的v9指令集和公版CPU IP。

ARMv9架构

如上图,ARM在v9的主要变化是2个增强,2个添加和1个兼容。

增强了:安全性和矢量处理

添加了:机器学习和数字信号处理

兼容了:ARMv8

安全性的增强

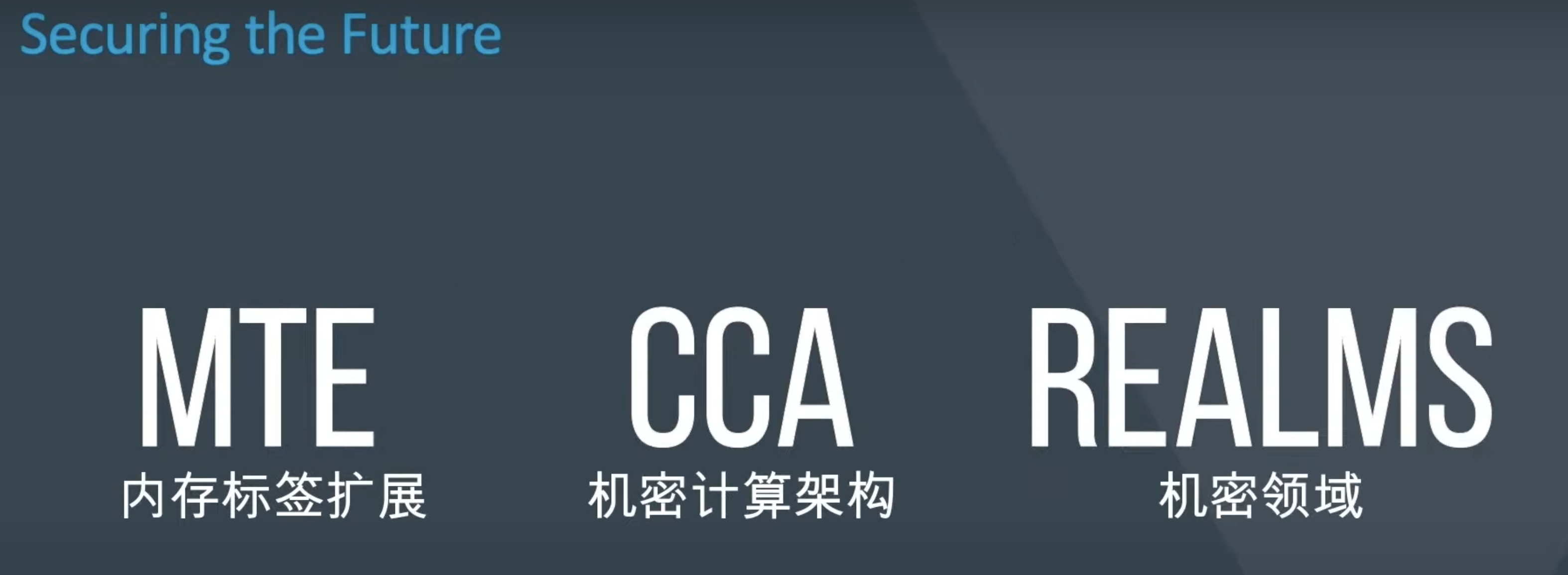

Armv9把安全性放在了第一位,在整个安全架构里有:MTE、CCA、REALMS。

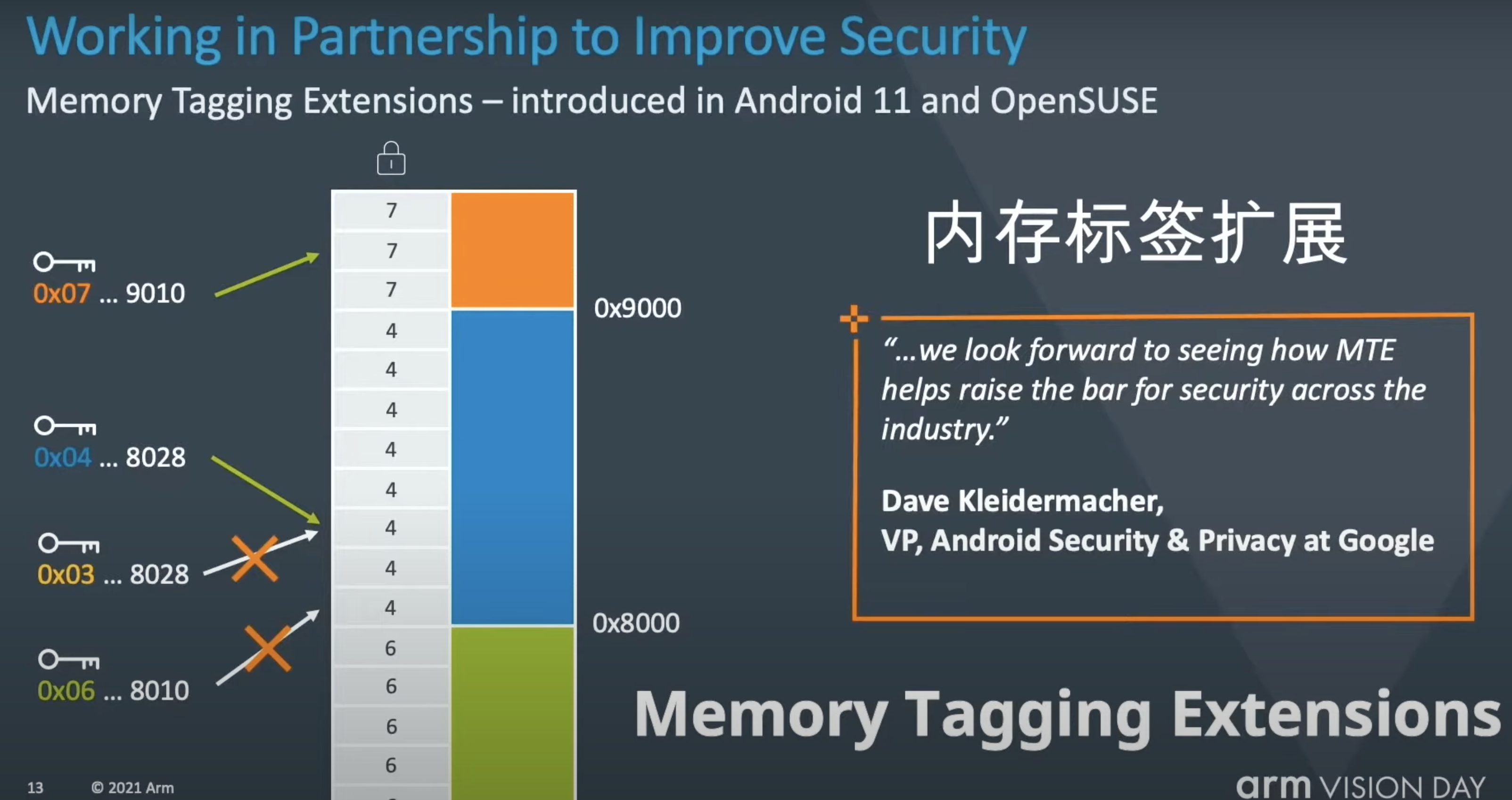

MTE

Arm MTE(内存标记)并不是v9的新功能,而是随v8.5一起引入的,MTE或内存标记扩展旨在帮助解决世界软件中两个最持久的安全问题。缓冲区溢出(Buffers overflows)和无用后使用(use-after-free)是持续的软件设计问题,在过去的50年中,这些问题一直是软件设计的一部分,并且可能需要花费数年的时间才能对其进行识别或解决。MTE旨在通过在分配时标记指针并在使用时进行检查来帮助识别此类问题。作为Armv8.5指令集的一部分引入。MTE现在内置于Arm 最近宣布的符合Armv9 的 CPU 中,例如 Cortex-X2、Cortex-A710 和Cortex-A510。基于Armv9 的 CPU 也将集成 MTE。还增加了一个Arm内存标签扩展(MTE),开发人员可以用“标签”锁定数据串,只有使用正确的密钥才能访问,该密钥由负责从内存中调用数据的代码“指针”持有,从而确保和保障数据的安全。

内存标记背后的想法非常简单:将一些位(4bit)添加到内存块中,以标识应用程序对内存的使用是安全的。Arm将内存标记实现为两阶段系统,也称为锁和钥匙:

- 地址标记。在进程中的每个指针的顶部添加四bit校验位(59-56)。地址标记仅适用于 64 位应用程序,因为它使用ARM64 feature TBI (top-byte-ignore)。地址标签充当虚拟“key”。

- 内存标记。内存标签也由四位组成,在应用程序使用的物理内存中16字节对齐。这四bit不用于应用程序数据,而是单独存储。内存标签是“lock”。

虚拟地址标签(key)必须与内存标签(lock)匹配。否则,会发生错误。

CCA

机密计算可以打造基于硬件的安全运行环境来执行计算,保护部分敏感数据和代码,甚至不受特权软件的影响。也就是说,即使是具有最高权限的设备操作系统也无法影响。虽然操作系统可以决定何时运行,但应用程序位于独立的硬件保护内存区域,和系统中的一切是隔离的。这意味着就算社交媒体应用真的感染了恶意软件,也不会传播给设备里的其他部分。CCA的目标是从当前的软件堆栈情况中获得更大的收益,在当前的软件堆栈情况下,在设备上运行的应用程序必须固有地信任它们所运行的操作系统和虚拟机管理程序。传统的安全模型是基于以下事实建立的:更高特权的软件层被允许查看较低层的执行,然而当操作系统或系统管理程序被以任何方式损害时,这就可能成为了一个问题。

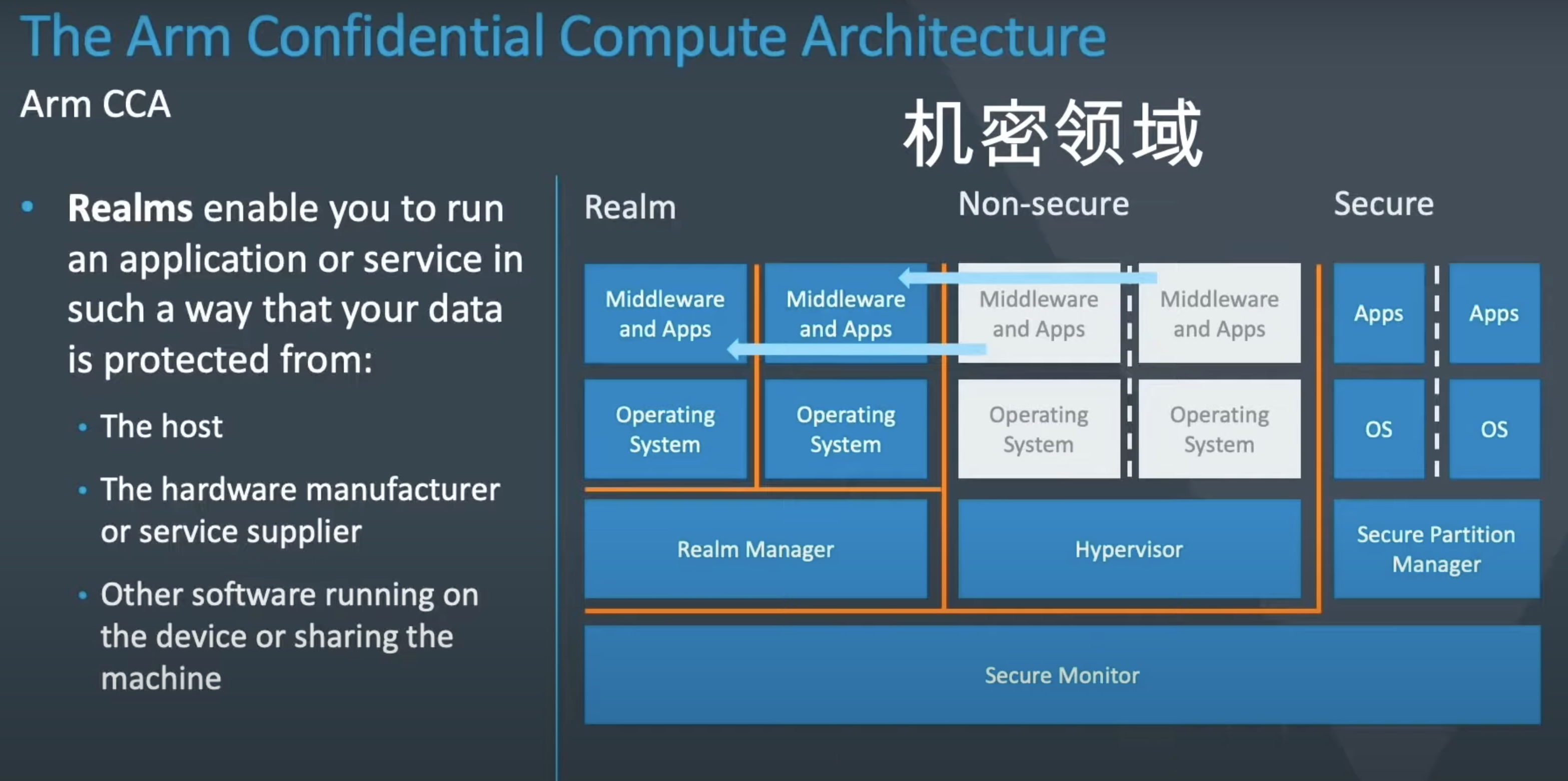

CCA引入了动态创建““realms”的新概念,可以将其视为对OS或虚拟机管理程序完全不透明的安全容器化执行环境。系统管理程序将仍然存在,但仅负责调度和资源分配。而“realm”将由称为“ealm manager”的新实体管理,其被认为是一段新的代码,大致大小约为hypervisor的1/10。

realm内的应用程序将能够“证明”领域管理器以确定其是否可信任,这对于传统的虚拟机管理程序而言是不可能的。

REALMS

机密领域(Realms)则是面向所有应用,运行在独立于安全或非安全环境之外的环境中,实现保护数据安全的目的,在传输中和休息时保持数据加密,并在使用时被硬件隔离,在云环境中,也意味着保护物理CPU以及运行在第三方代码旁的虚拟化处理器。

使用realms的优势在于,它极大地减少了设备上运行的给定应用程序的信任链,并且OS对安全性问题变得越来越透明。与当今需要企业或企业使用带有授权软件堆栈的专用设备的情况相反,需要监督控制的关键任务应用程序将能够在任何设备上运行。

矢量的增强

ARMv9的另外一个重要的特性就是SEV2指令集的加入。SVE2是作为NEON的后继产品,我会单独写一篇文章来讲解。本篇主要介绍SVE2的增强功能。

可伸缩矢量扩展(SVE)的于2016年首次亮相,并首次在富士通的A64FX CPU内核中实现,该芯片已为日本排名第一的超级计算机Fukagu提供支持。SVE的问题在于,新的可变矢量长度SIMD指令集的第一次迭代的范围相当有限,并且更多地针对HPC工作负载,缺少了许多仍由NEON涵盖的更通用的指令。

SVE2于2019年4月发布,旨在通过用所需指令补充新的可扩展SIMD指令集来解决此问题,以服务于类似DSP等目前仍在使用NEON的工作负载。

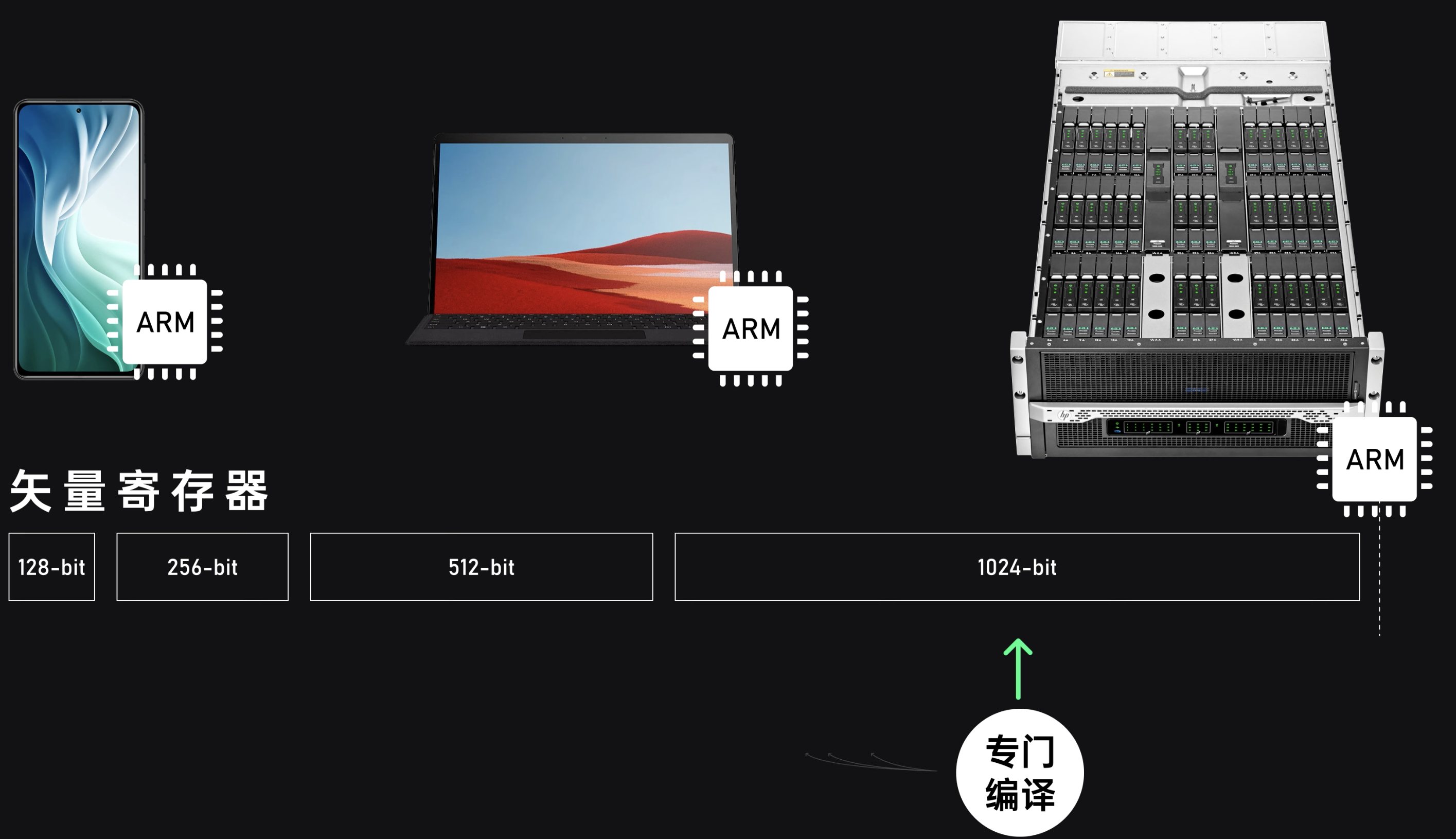

除了增加的各种现代SIMD功能外,SVE和SVE2的优势还在于其可变的向量大小,范围覆盖了128bits到2048bits,让其无论在什么硬件运行,都允许向量的可变粒度为128b。如果纯粹从向量处理和编程的角度来看,这意味着软件开发人员将只需要编译一次其代码,并且如果将来某个CPU带有本地的512b SIMD execution pipelines,该代码将能够充分利用单元的整个宽度。同样,相同的代码将能够在具有较低硬件执行宽度能力的保守设计上运行,这对于Arm设计从物联网、移动到数据中心的CPU而言至关重要。在保留Arm体系结构的32bits编码空间的同时,它还可以完成所有这些工作。然而类似X86这样的架构则需要根据矢量尺寸增加新的指令和扩展。

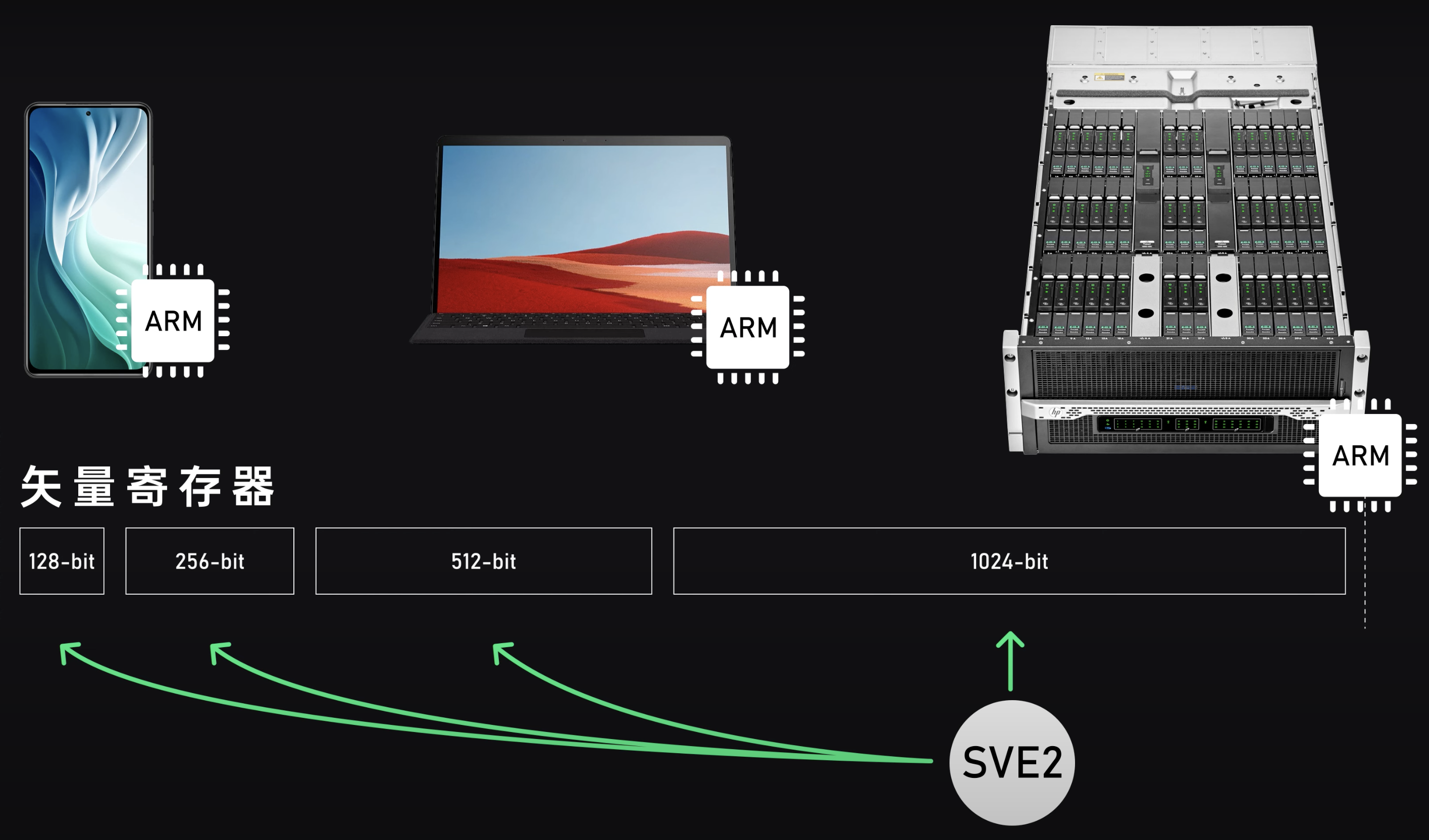

如上图,以往我们手机上的,桌面端的,还有超算伺服器上的ARM处理器虽然都是ARM处理器,但是它们的矢量寄存器的宽度是完全不一样的。例如,手机芯片支持*128位矢量长度,桌面端可能有256位,而超算服务器上面能达到512位甚至1024位。这就意味着,给超算设计的程序是无法轻易的在手机上运行的。有了SVE2后,情况就不同了,它打破了矢量长度的限制,开发者只要编译一次,app就可以同时在手机芯片,桌面芯片和服务器芯片上运行*。所以,以后一些给超算设计的算法,在手机上也可以更容易的跑起来。这个对ARM生态的构建非常有利,它拉通了不同平台的差异性,也能看出ARM想要不断你的占领PC和超算服务器市场。

三款公版处理器

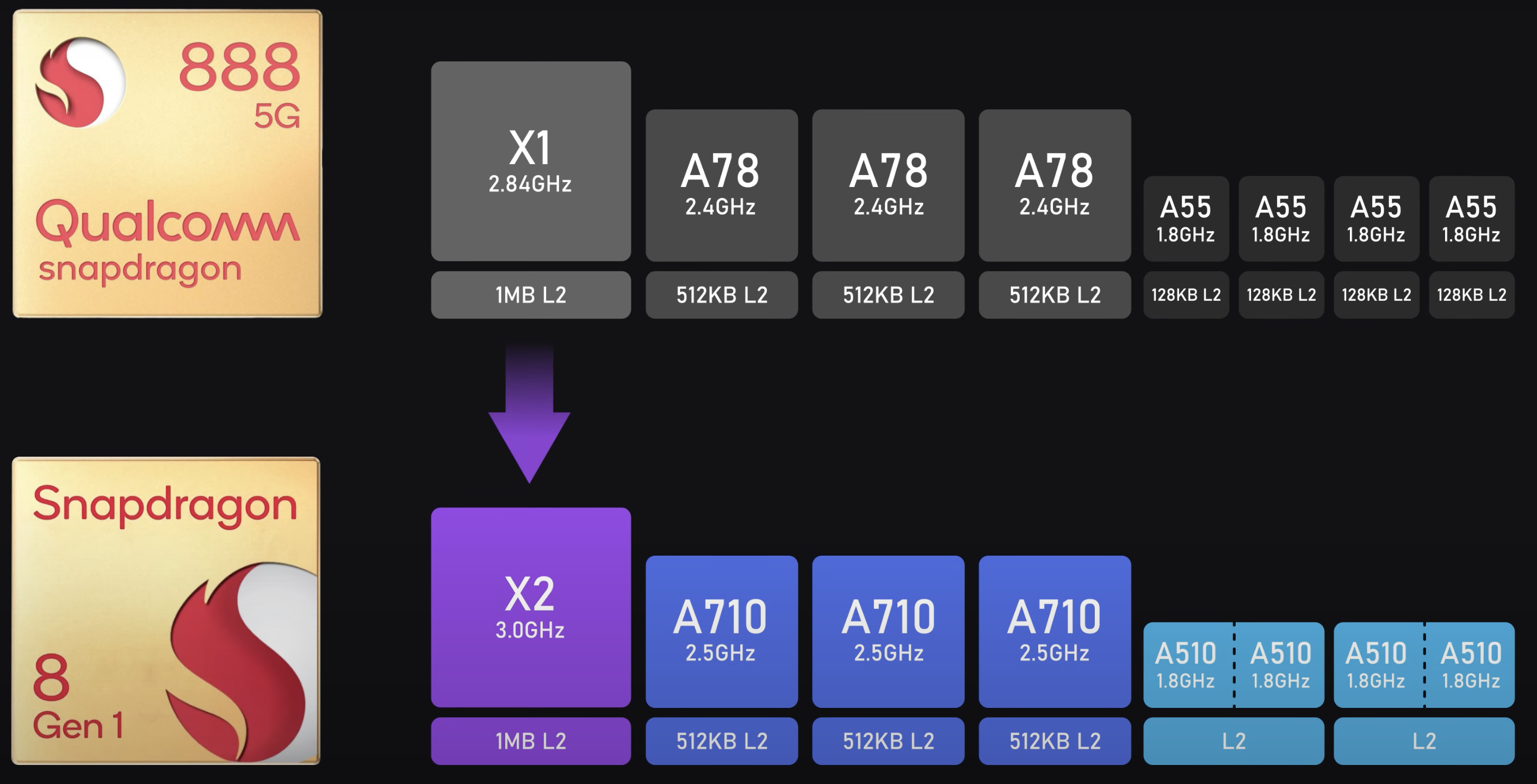

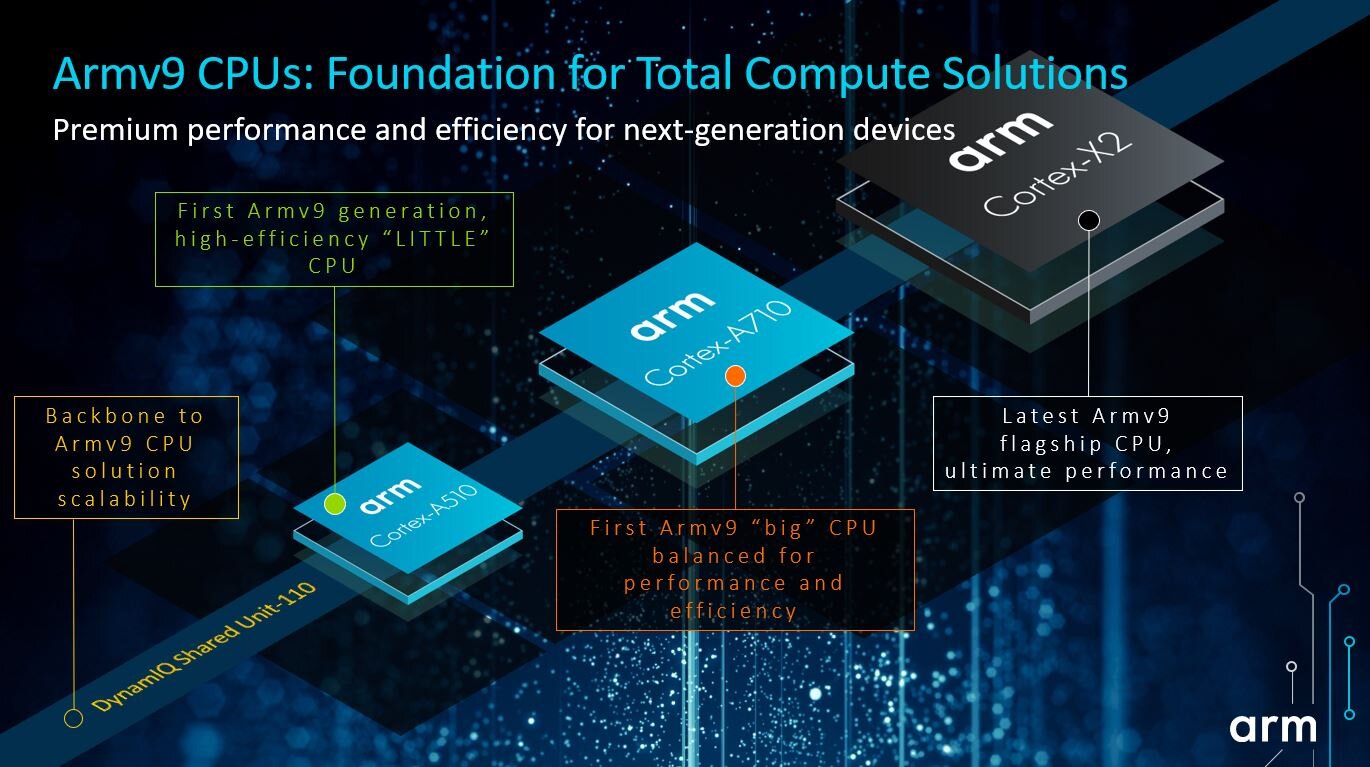

在ARMv9公布两个月后,ARM又公布三款公版CPU。

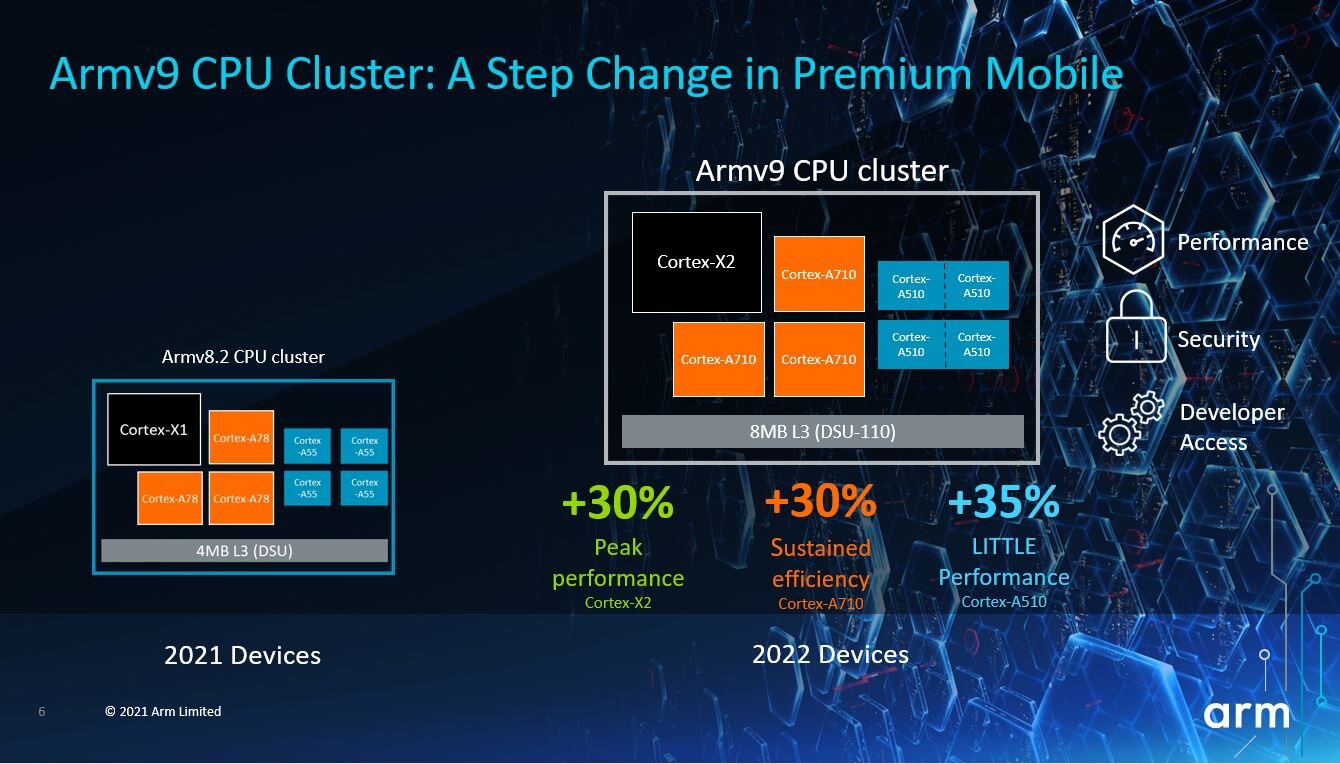

- 一个X2: 超级性能核,X1的下一代。由美国奥斯汀团队设计。

- 3个A710: 注重能耗比的大核,A78的下一代。由美国奥斯汀团队设计。

- 4个A510:能耗小核,继A55四年后的第一次重大改进,由英国剑桥团队设计。

L3 Cache 也从v8 的CPU的4MB升级到了8MB。

ARM声称:使用了1个X2和3个A710和4个A510设计的SoC,相当于2020年的旗舰芯片骁龙888,Exynos2100的30%的峰值性能提升,或者同样性能下的30%的能耗降低。那么它是怎么做到的呢?我们来看一下ARM公布的PPT。

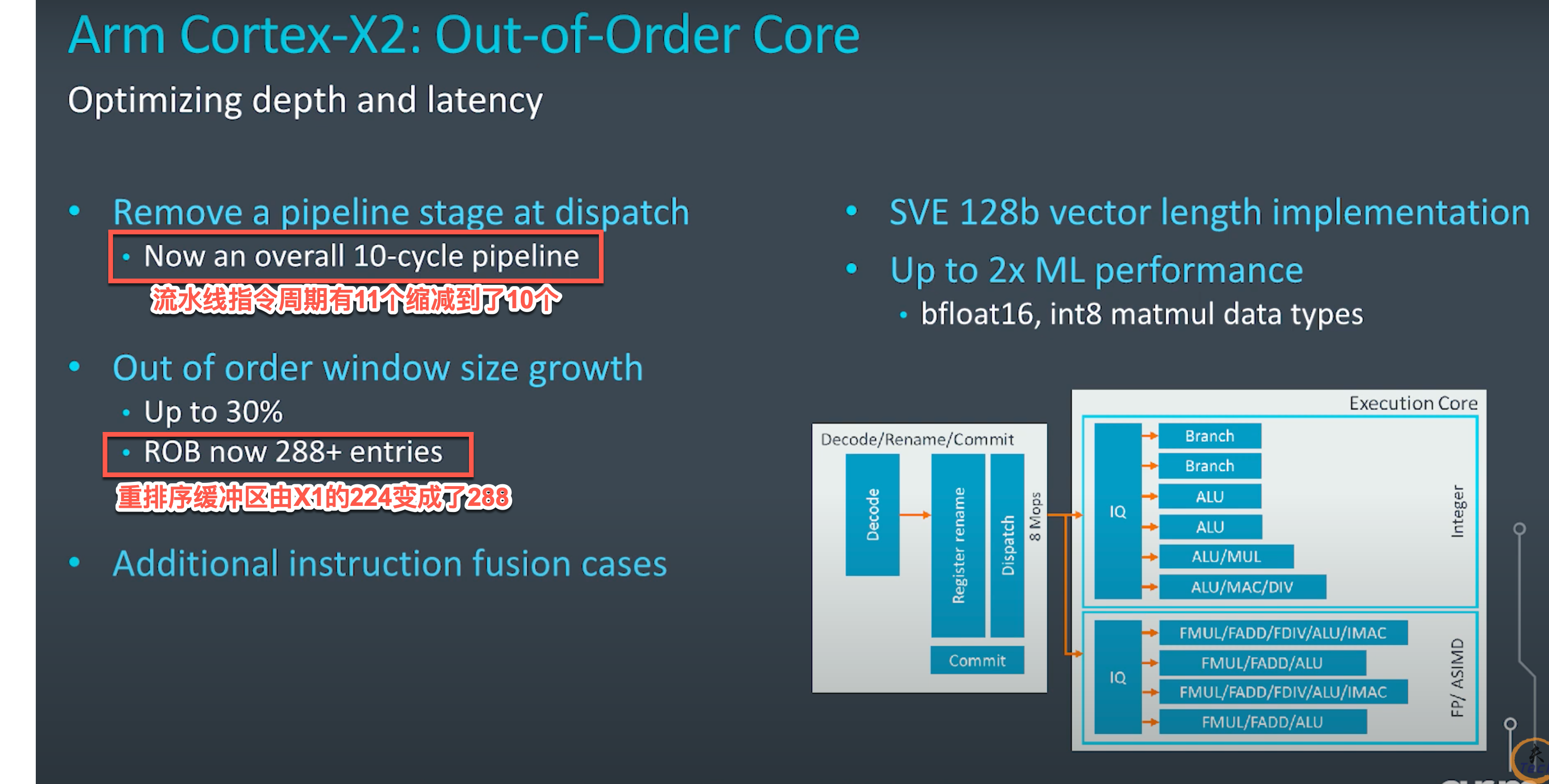

超级性能核X2

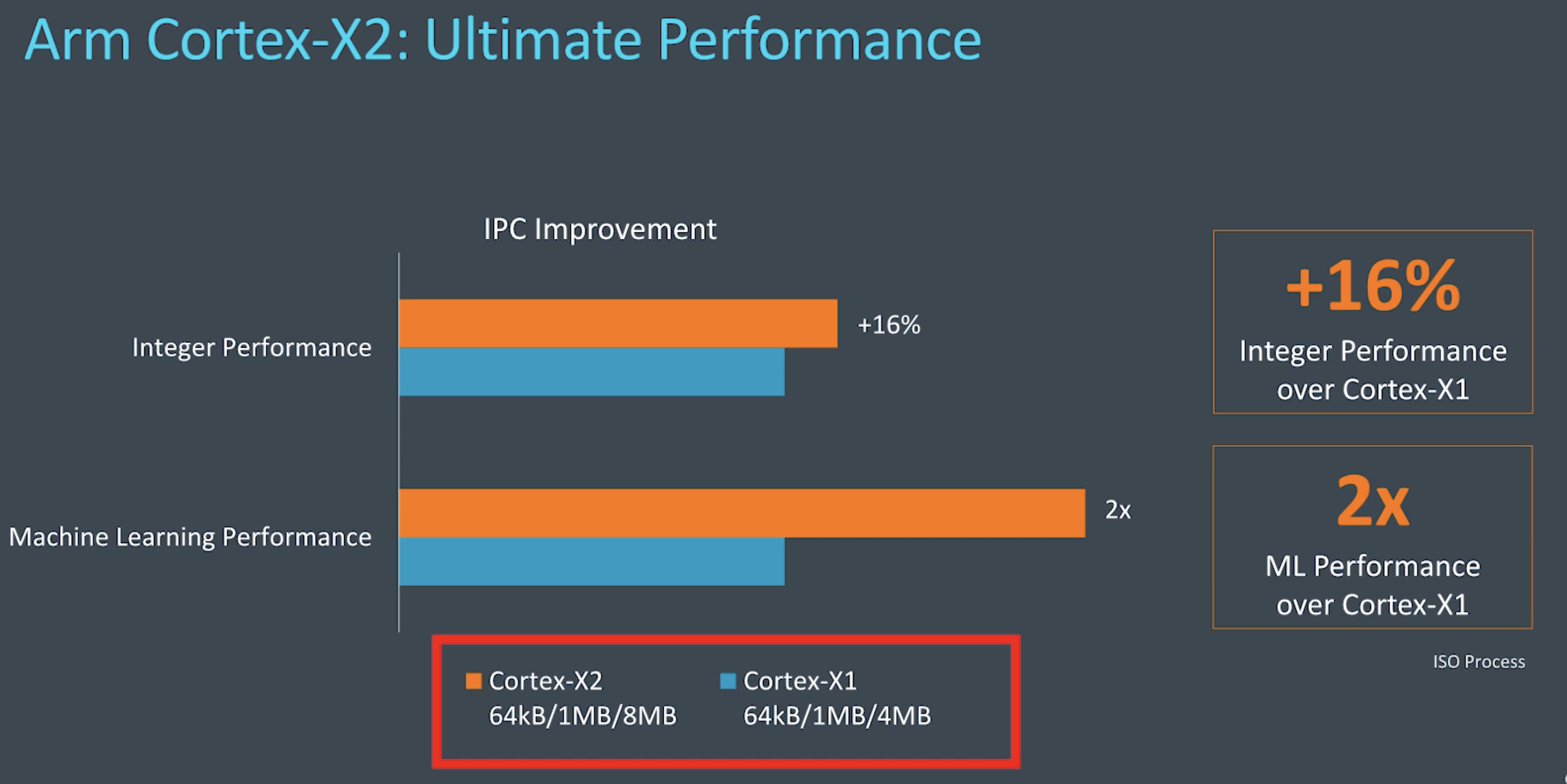

在相同的制程下,X2可以得到16%的IPC提升,但是值得留意的是相比X1 的 4MB的L3 Cache, X2的L3 Cache变成了8MB Cache。

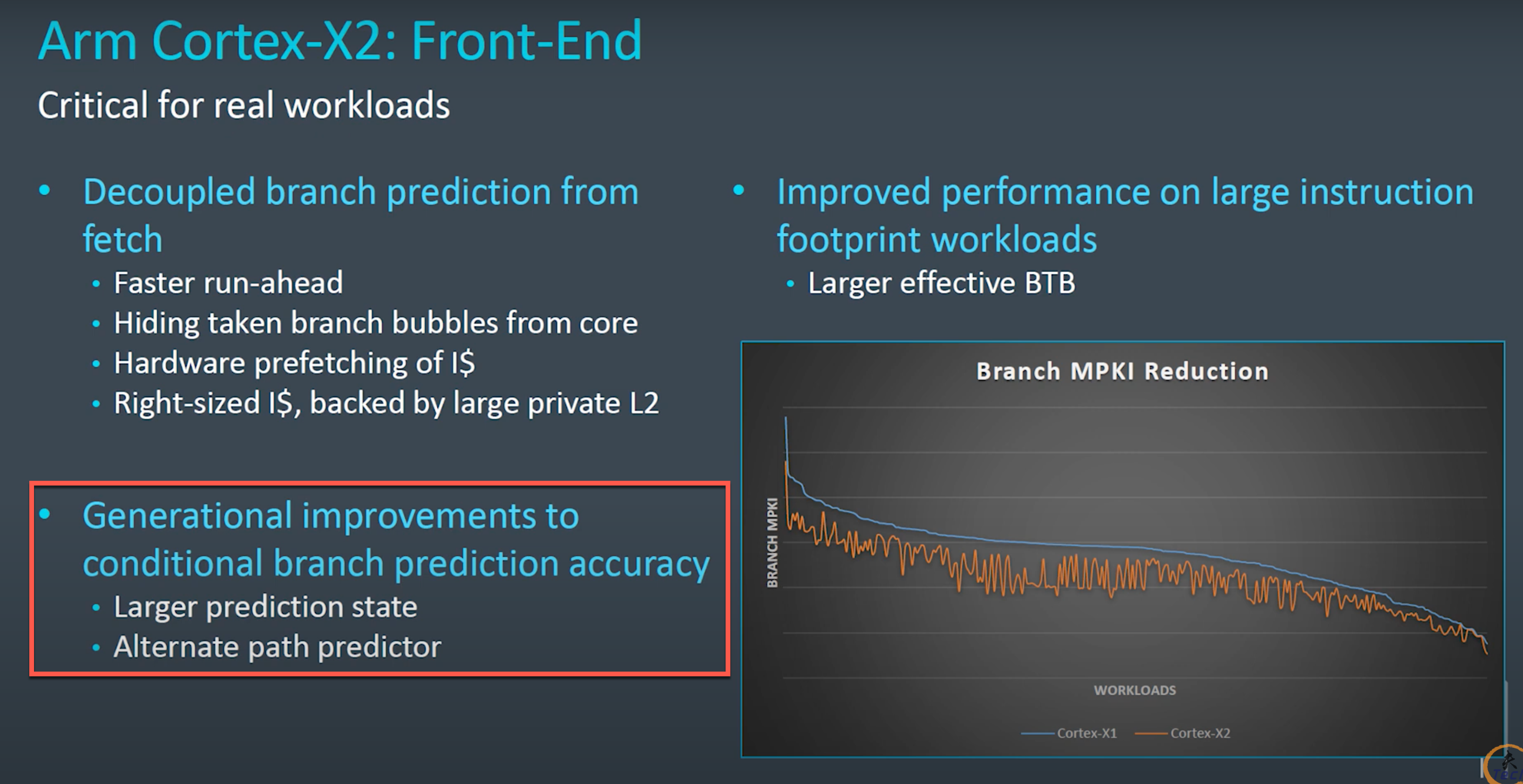

同时X2的前端提高了分支预测的精度,重排序缓冲区由X1的224增加到了288,流水线长度从11个指令周期缩减到了10个。

并且还将二级缓存的转译后备缓冲器加大,数据预读取功能增强。所以,不难发现,X2的性能提升主要靠的是:

- 提高缓存大小

- 加强访存性能

- 优化进程间通信延迟来实现的

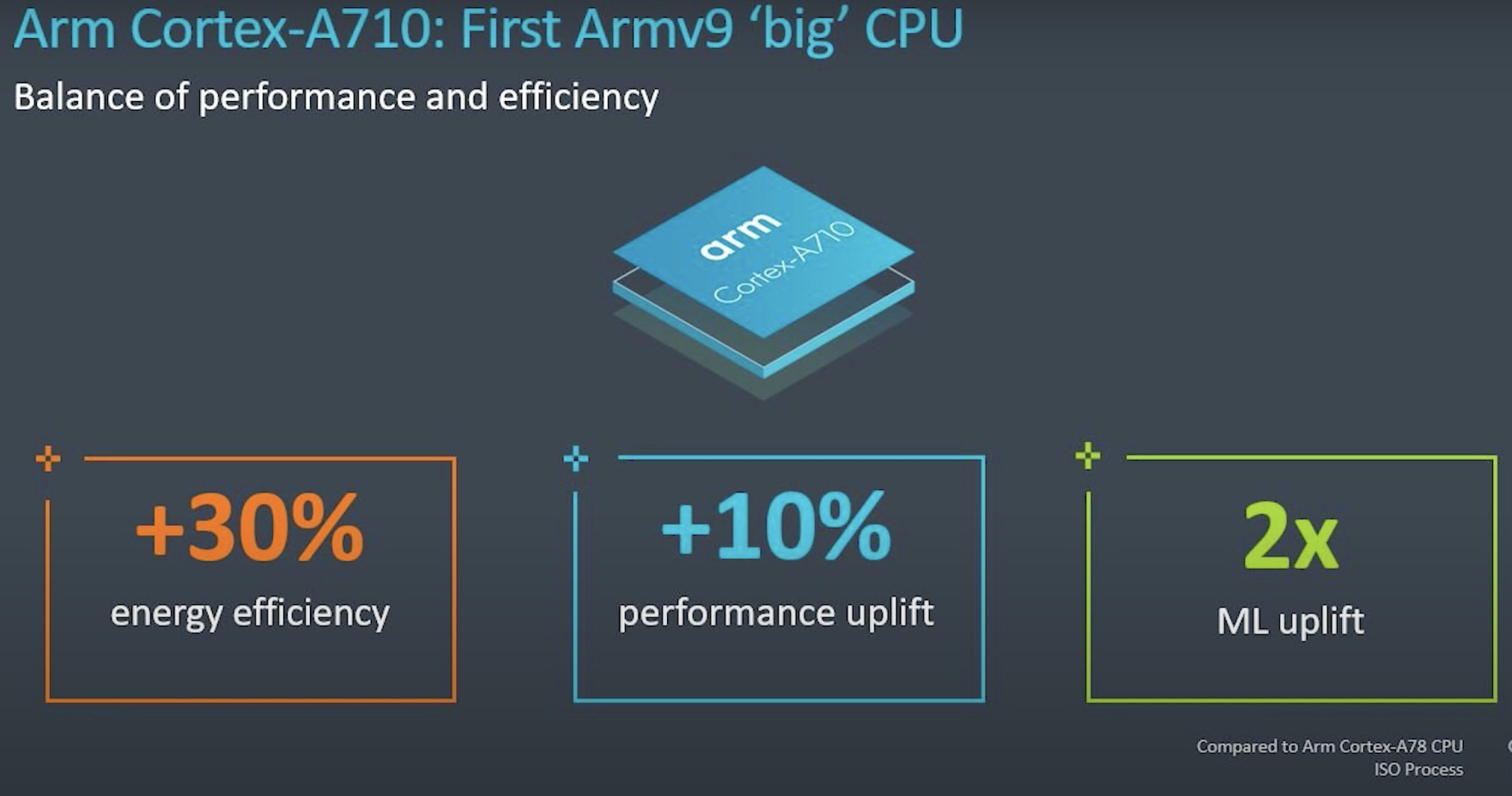

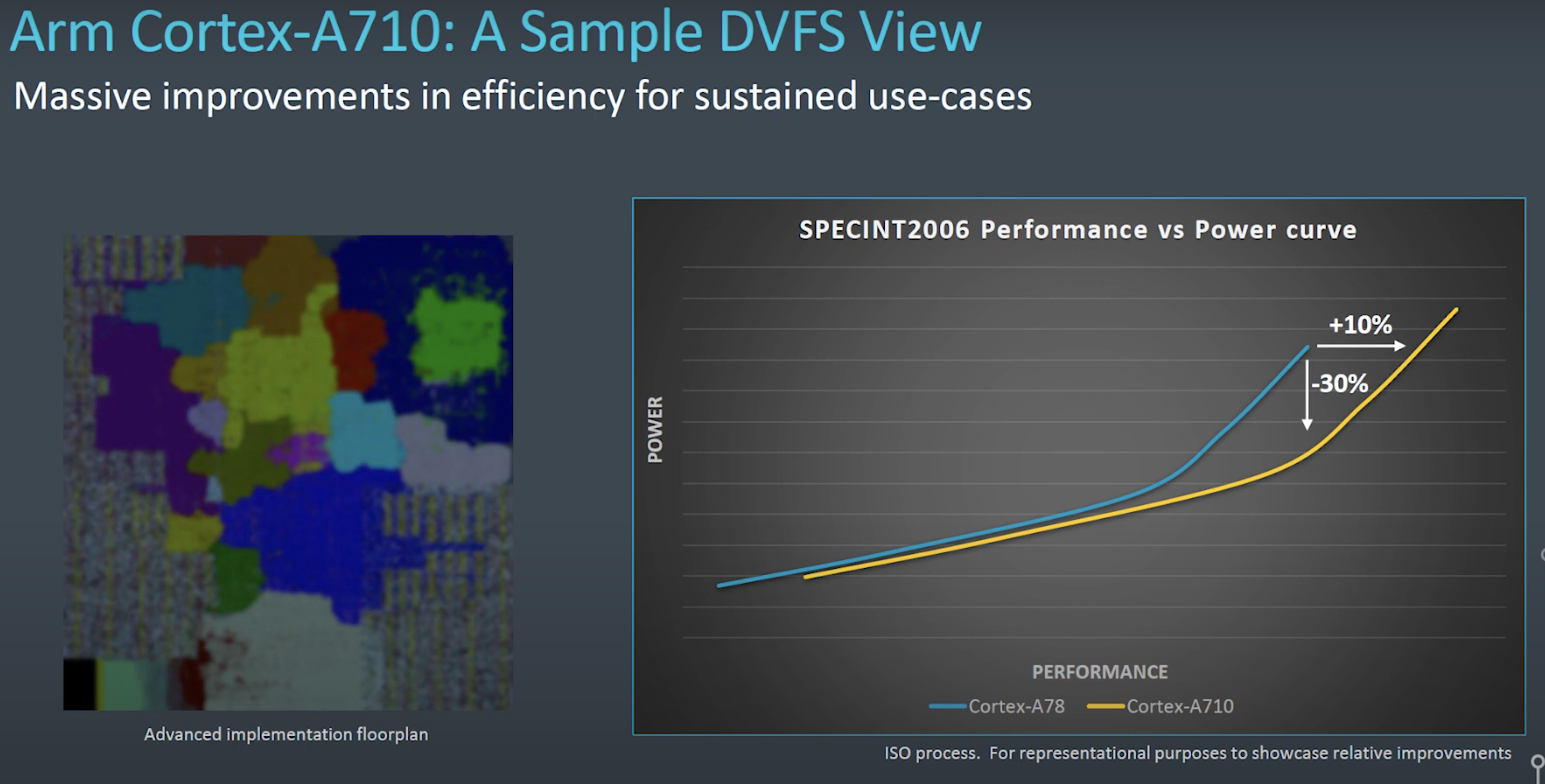

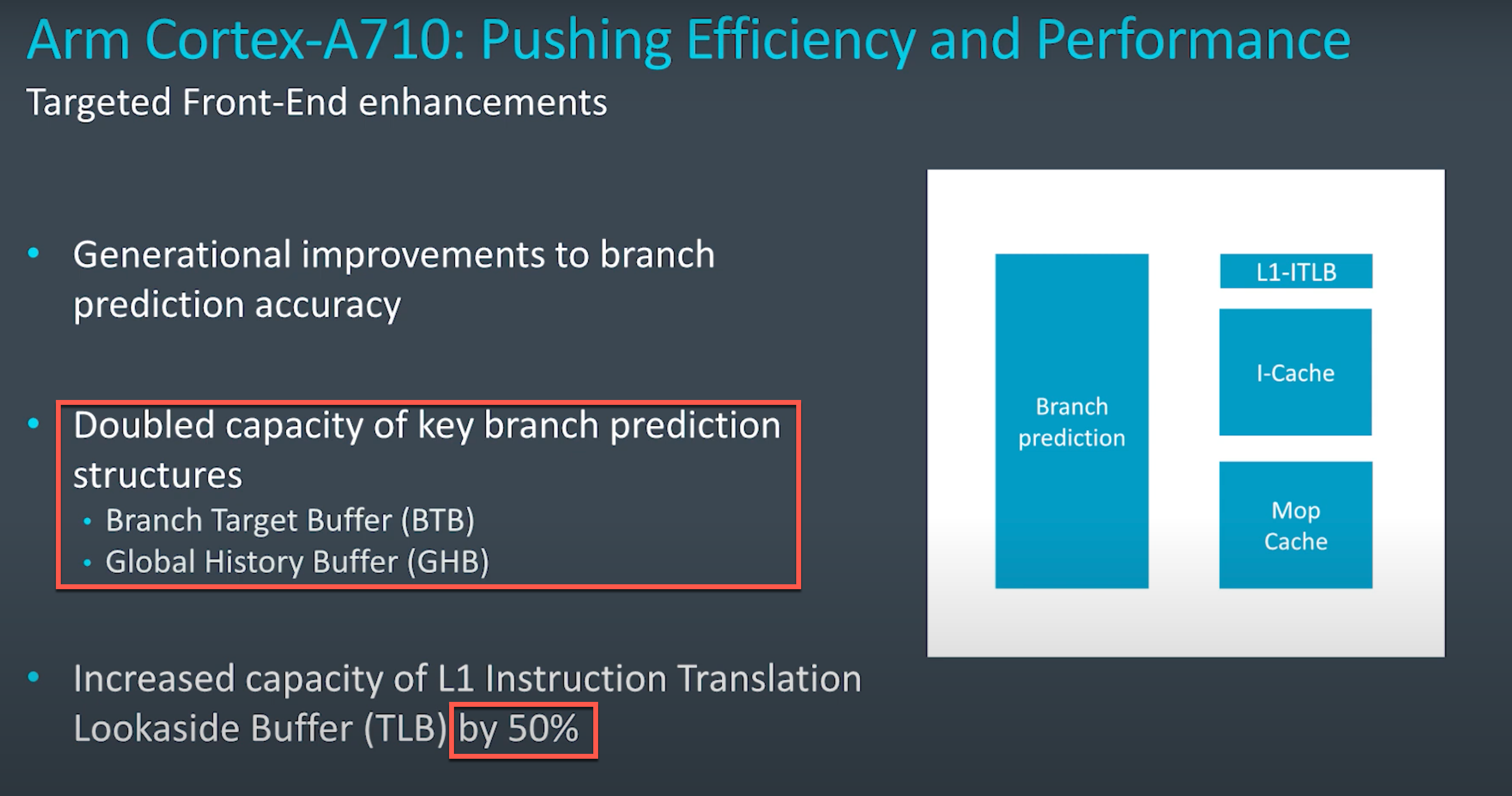

注重能耗比的大核A710

ARM推出注重性能X系列大核后,传统的注重性能的7系列的大核就逐渐变成了注重能耗比的中核。A710相比上一代的A78只有10%的IPC提升,这还是在三级缓存翻倍的情况下实现的。

不过在功耗控制方面,A710要远远优于上一代的A78。在同样的性能下,A710相比A78还能再降低最多30%。

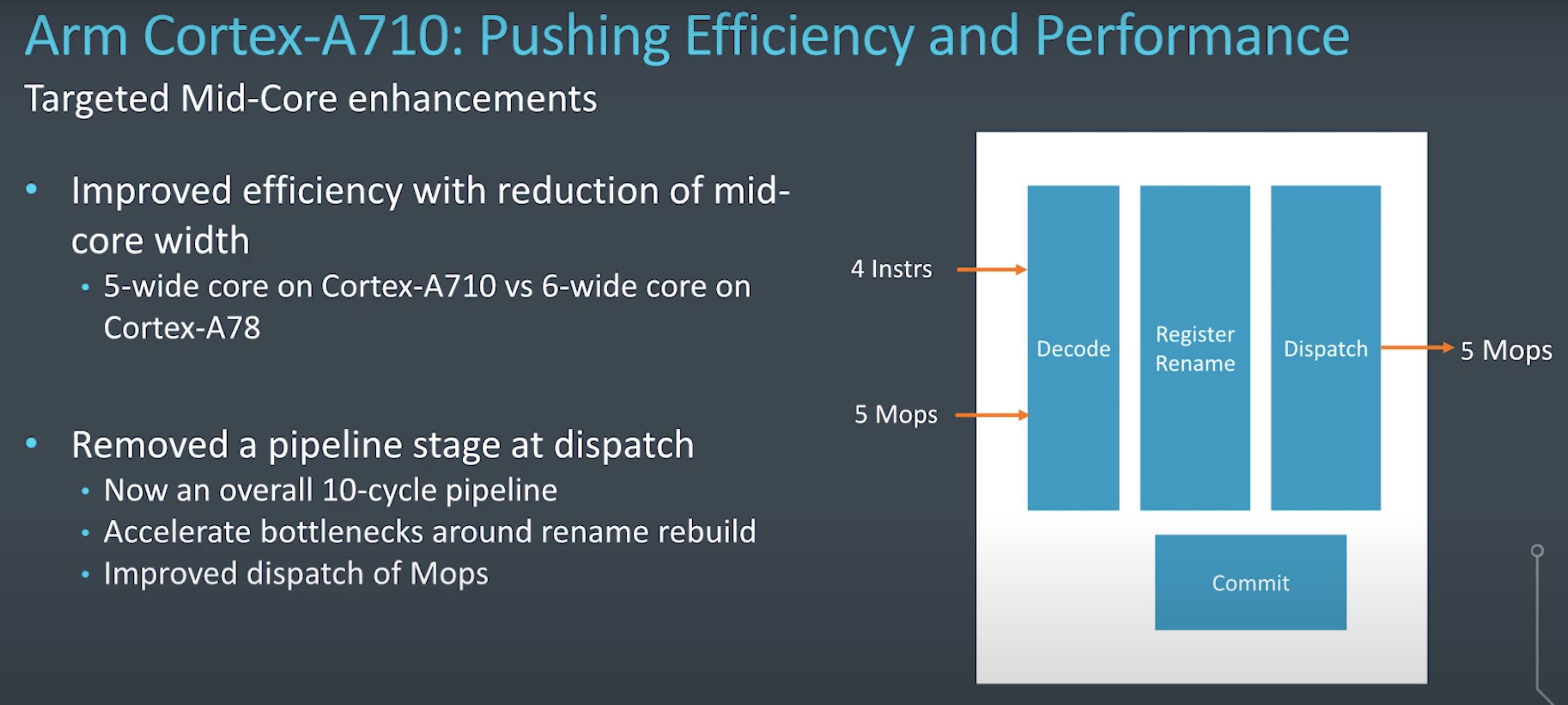

因为A710跟X2同为美国的奥斯汀团队设计,其设计理念基本相似:改进了分支预测并且加大了Buffer,优化了延迟,流水线的长度同样降至了10个周期。

同时为了进一步的降低能耗,A710的分发吞吐量从A78的6发射降到了5发射。A710的IPC性能提升不明显,只有10%的提高,很有可能就是因为发射数降低导致的。可以猜想,奥斯汀团队或许认为:更佳的能耗比才是A710的定位吧。所以,7系列的中核更可以被认为是更关注能效的中核了。

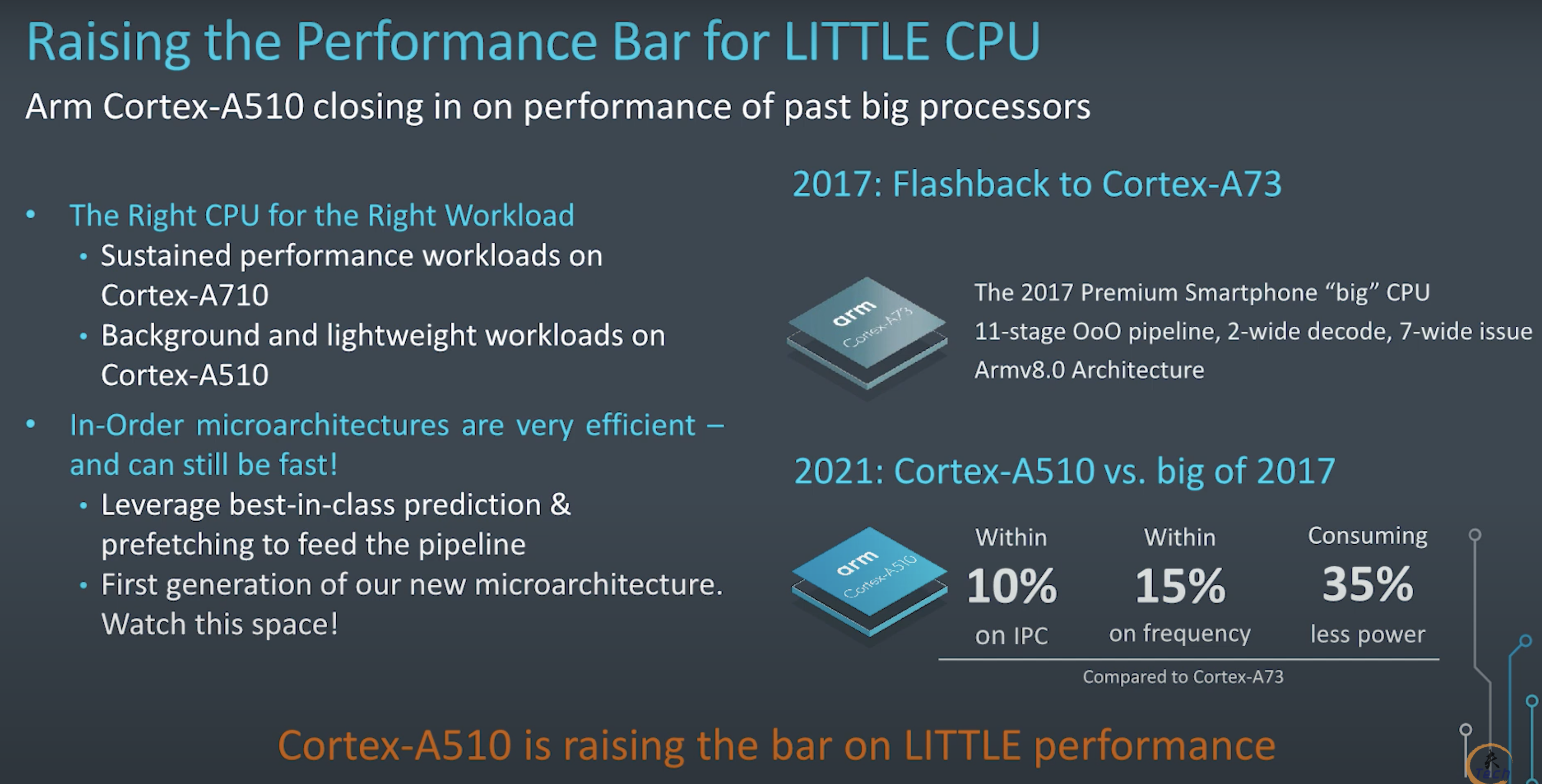

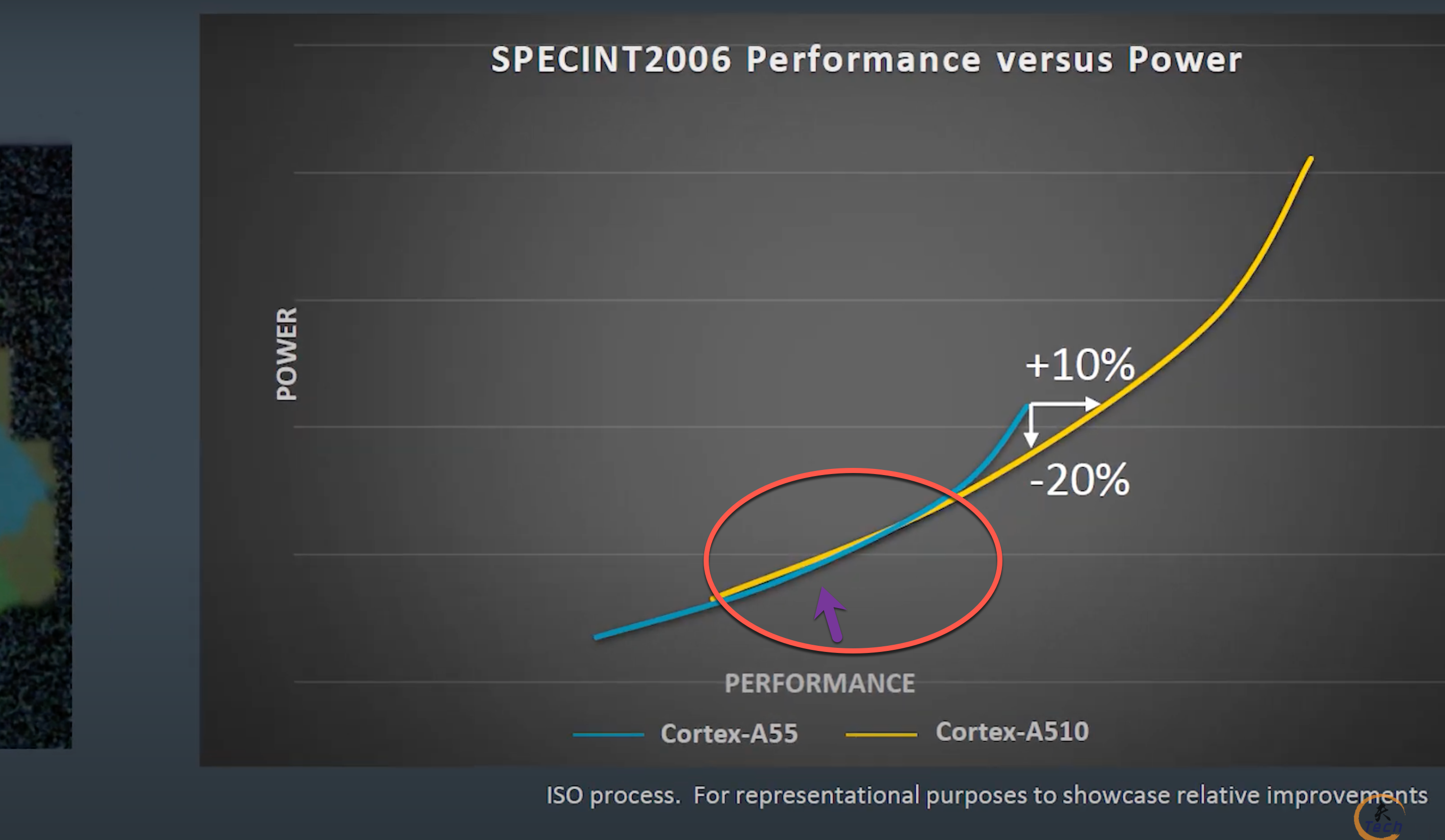

能耗小核A510

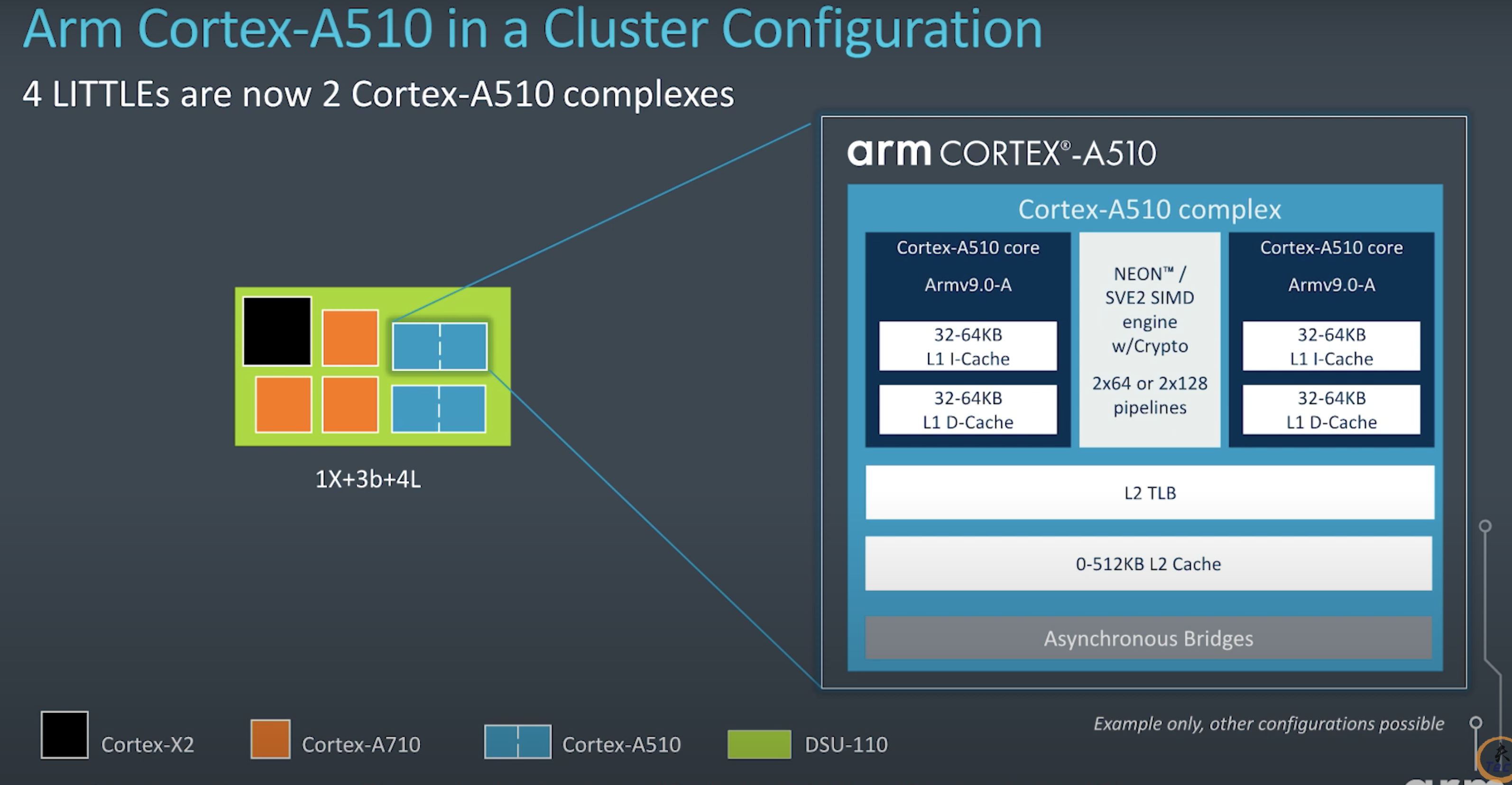

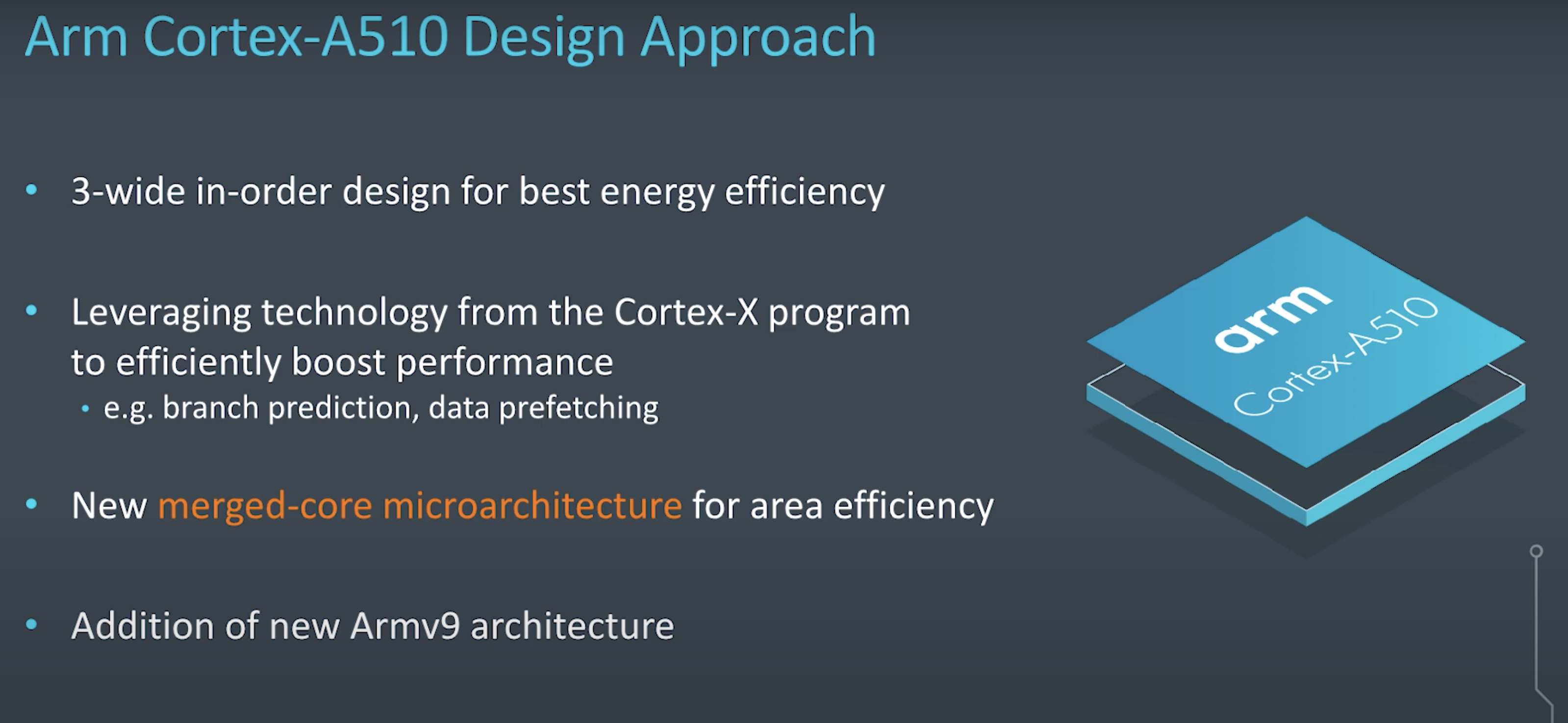

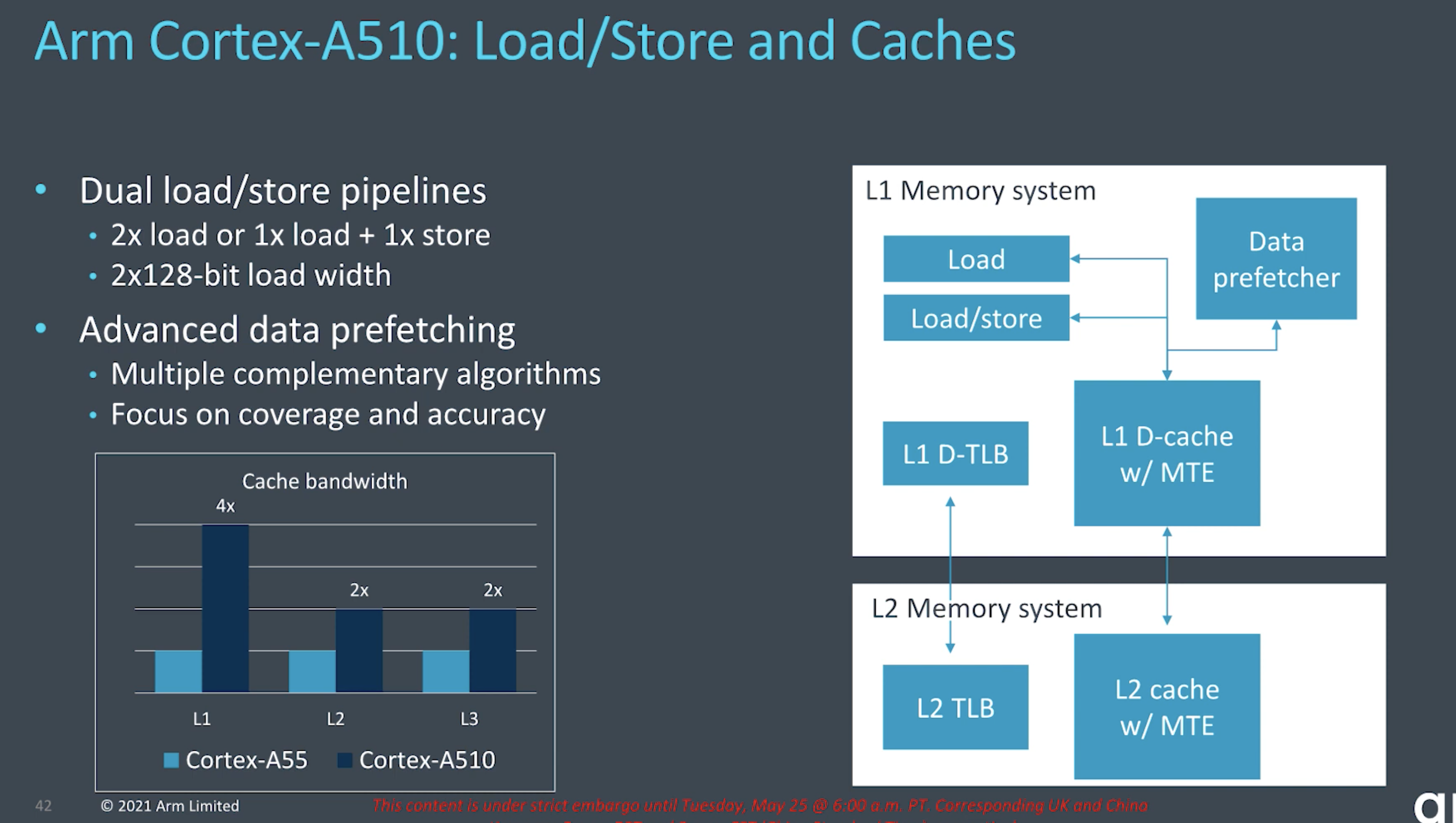

对比X2,A710,本次最抢眼的设计还属由剑桥团队设计的全新小核A510。A510在结构上做了重新的设计。由两个A510组成一个核心对,共享L2 Cache和浮点运算单元。这种设计可以理解为硬件超线程。

重点是,作为小核的A510的前端指令解码宽度,由双解码增加到3解码。

同时,A510的缓存带宽也提升了不少。L1 Cache带宽达到了A55的四倍;L2和L3 Cache的带宽达到了A55的两倍。

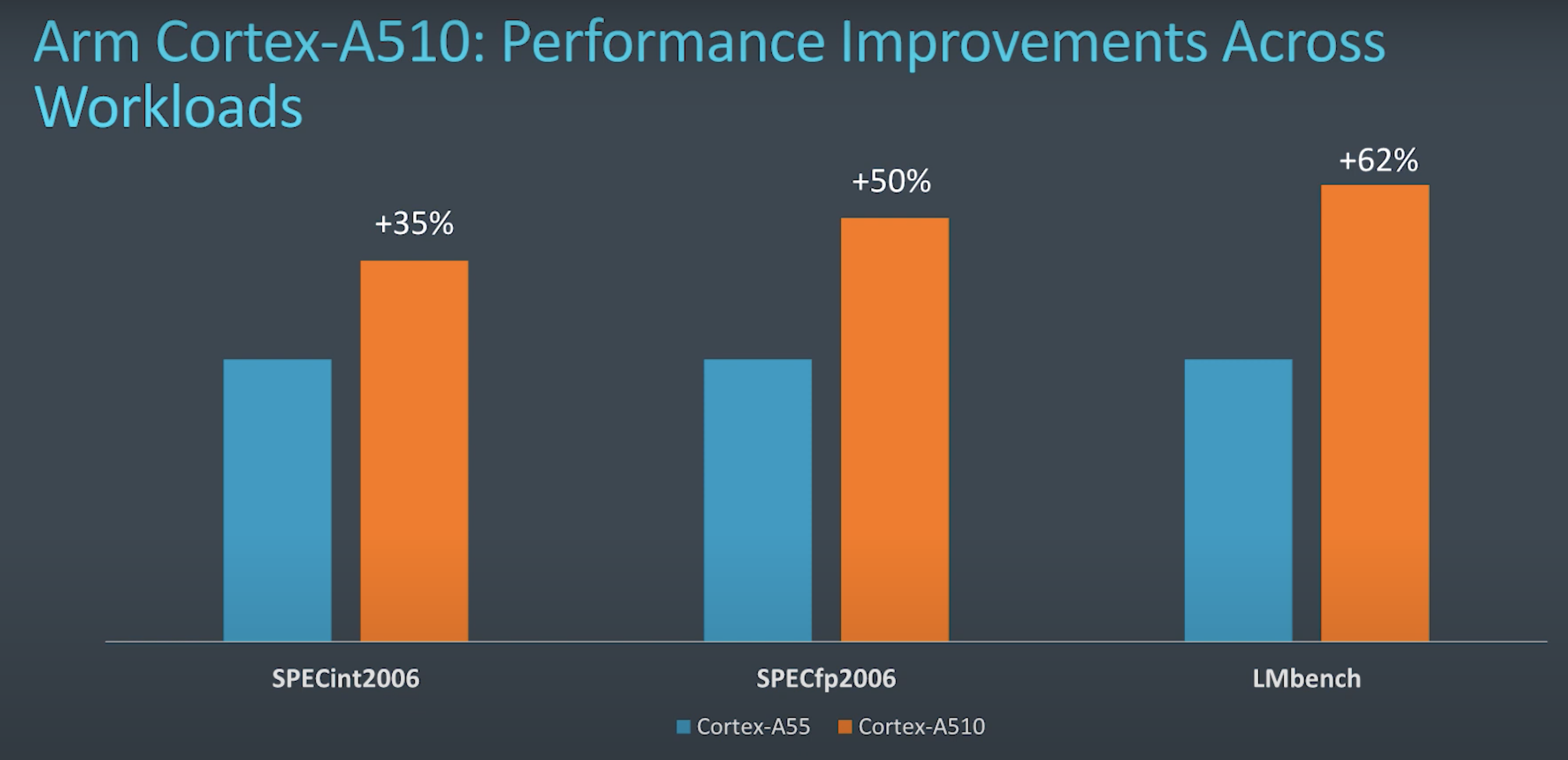

从ARM的PPT可以看出,A510相比A55有50%的浮点性能运算提升,和35%整数运算性能提升。 不过,A510相比A55的L2和L3的缓存尺寸也同样增加了一倍,所以,运算性能的提升也极有可能得力于缓存大小的增加。

不过,A510相比A55的L2和L3的缓存尺寸也同样增加了一倍,所以,运算性能的提升也极有可能得力于缓存大小的增加。

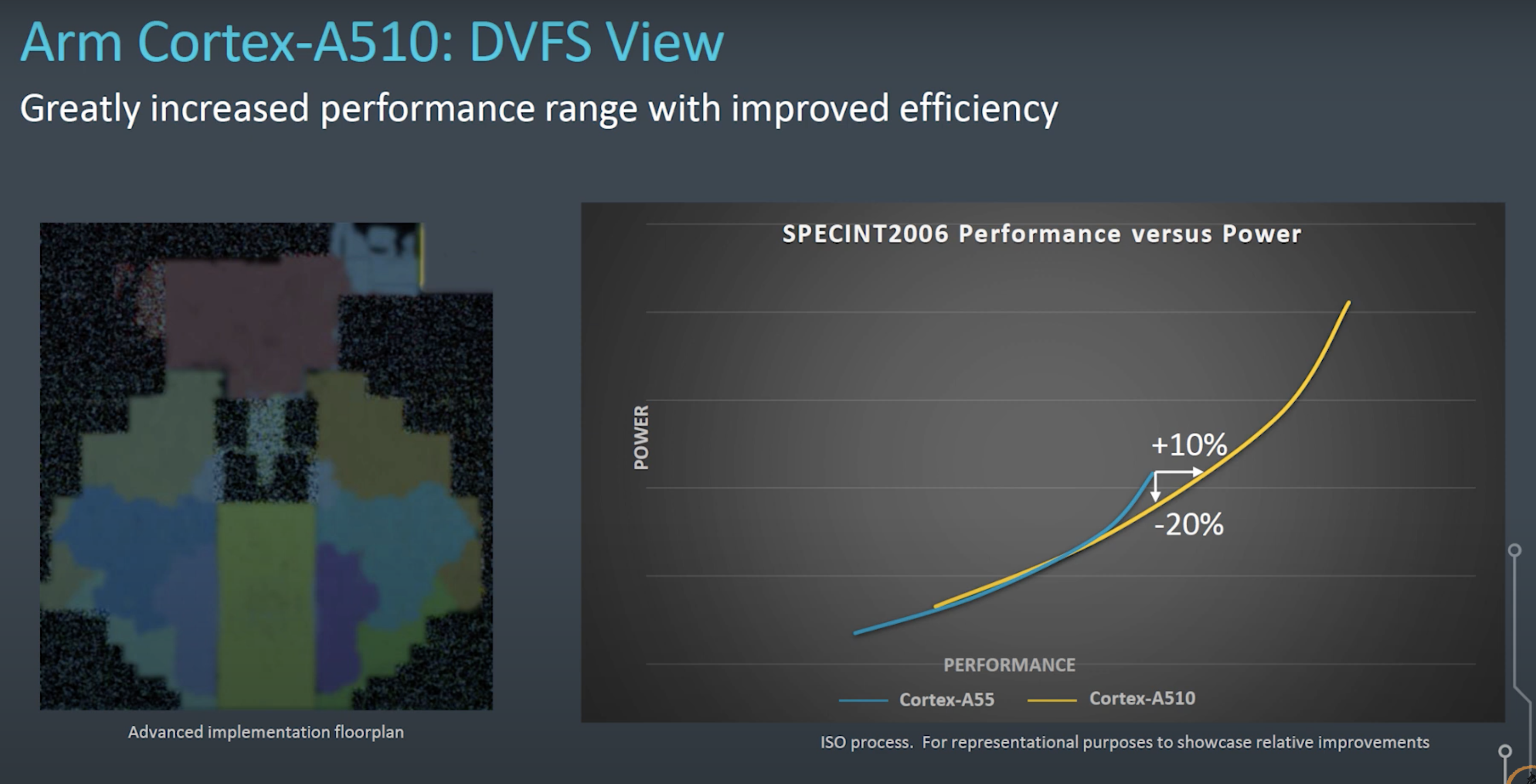

但是,从ARM的PPT看,有意思的是:A510只有在高频高能耗的情况下,才能跟A55拉开差距。对于一款主打能耗比的小核来说,多少这样的场景具体才能体现出能效收益还值得验证。

同时ARM宣称,A510可以以A73的65%的能耗达到90%的性能。剑桥团队或许是想通过提高小核A510的峰值性能,来承担更多的日常运算;同时保证在低负载下的功耗能维持在A55的水平,分担一部分A710和X2的运算压力,变相降低SoC的整体功耗,从而增加手机续航能力。

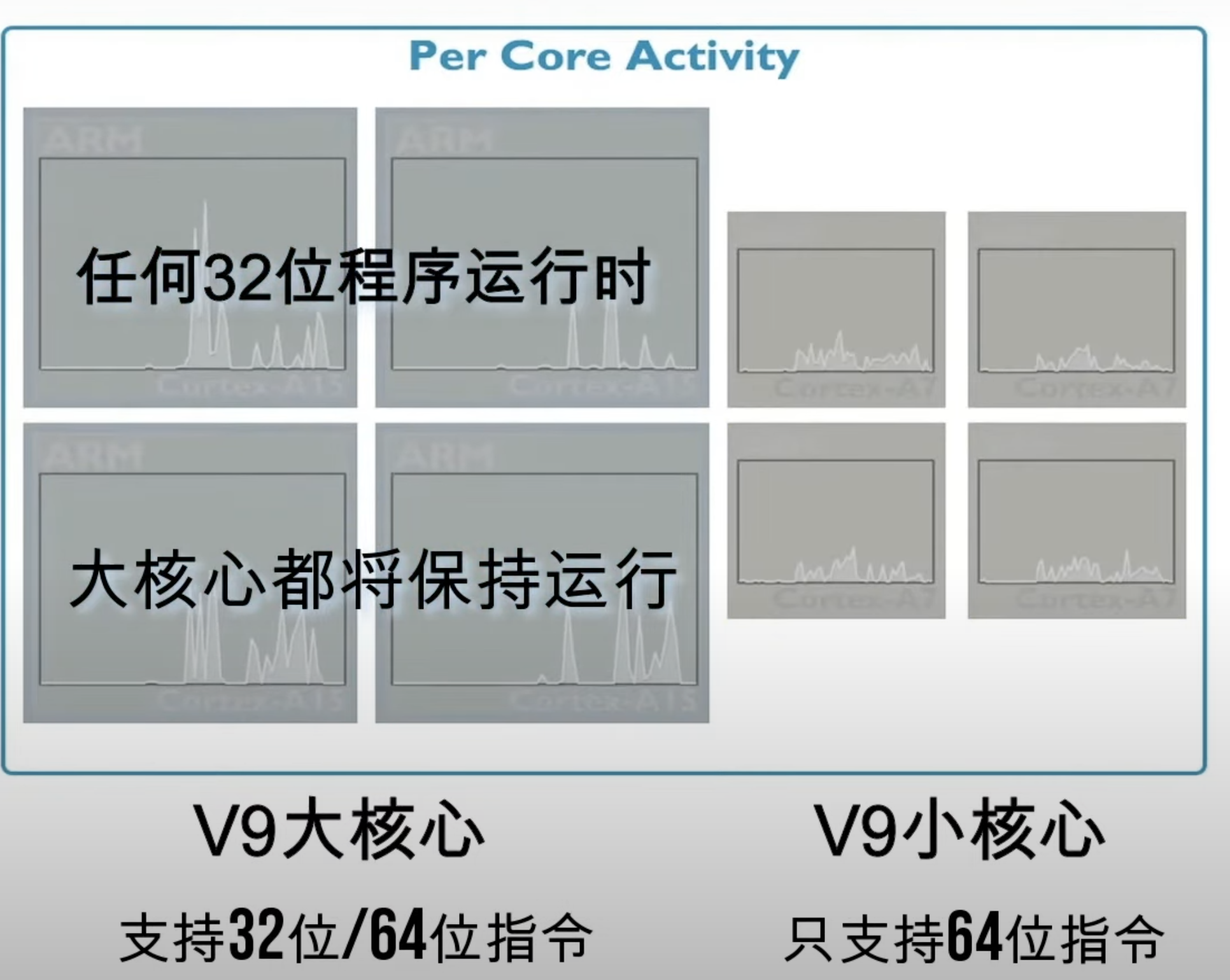

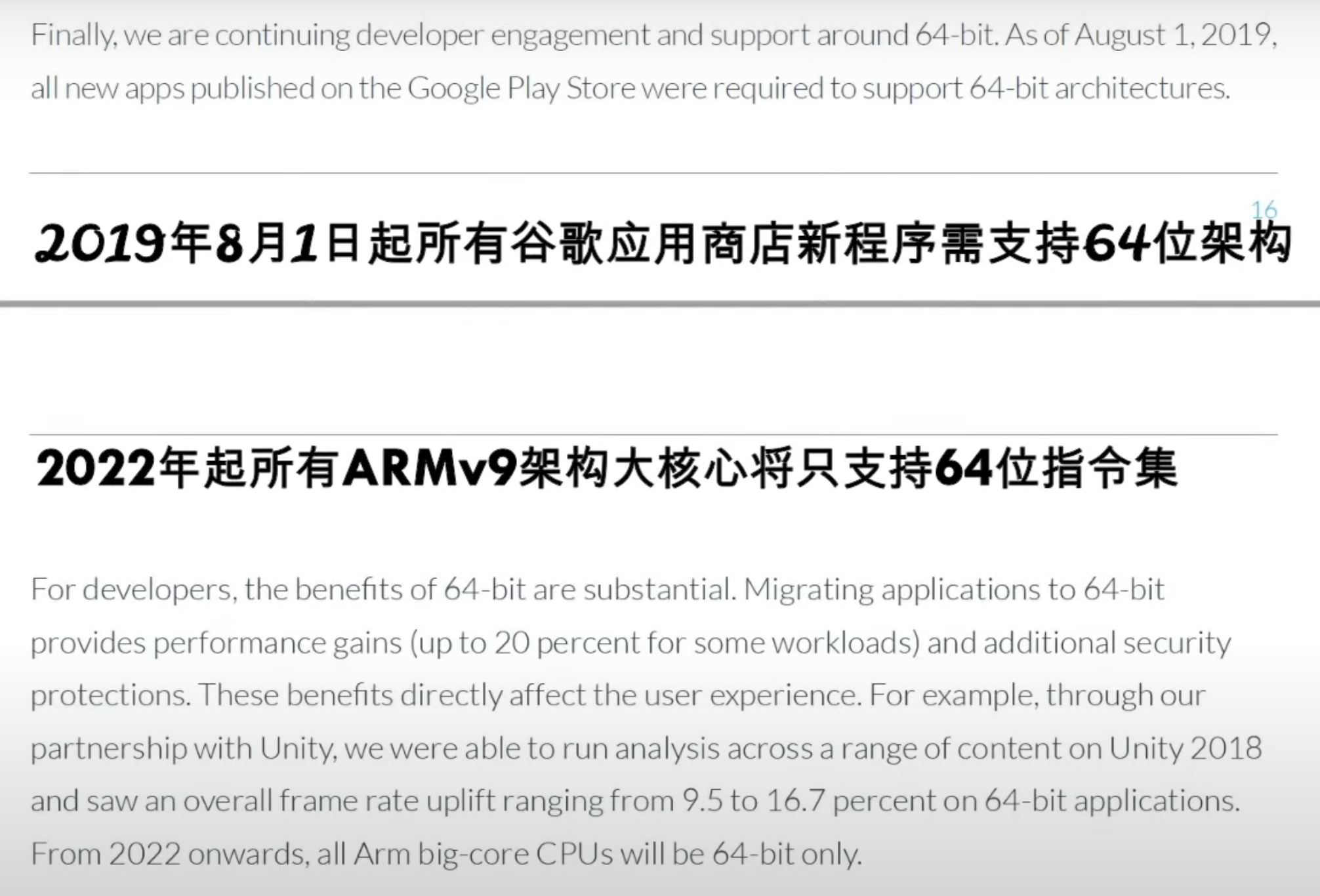

32位和64位的支持

本次发布的X2和X510完全放弃了对32位的支持,而中核A710仍旧兼容32位。ARM声称这是为了照顾中国大陆的安卓软件环境,现在市面上还有很大一部分软件包括:QQ、百度网盘、支付宝、网易云等仍旧是32位。

我们知道ARMv8是第一个支持64位指令集的架构,但是ARMv8同样也兼容32 bits App。这种兼容32位指令集的设计好不好呢?好的就是做到了向前兼容,不好的就是“任何32位程序运行时,大核心都将保持运行”。系统会有个调度器,当运行32位程序的时候,会自动分配大核给运行。所以本来是需要跑在小核的32位程序,现在都需要跑在A710的大核上了,这样就会造成额外的电力损耗。

所以为了解决这个问题,ARM公司的白皮书里宣布:“2019年8月1日起,所有的Google应用商店的新程序必须支持64位架构,2022年起所有的ARMv9架构的大核心只支持64位指令集。”

总结

总的来看,2021年发布的三款公版CPU core,性能提升十分有限,X2和A710都没有对核心结构进行大刀阔斧的改动,而是通过增加Cache提升计算性能和一系列的优化来进一步降低功耗,本质上还是对之前A76的深度优化。虽然A510核采用了全新的设计,但是在低负载下功耗甚至高出A55。估计要想看到X和A7xx核的结构性的设计更新,还要看2022年法国的索菲亚团队是不是能推陈出新了!

2021年底联发科的天玑9000和高通的Snapdragon 8 Gen1 都采用了ARMv9指令架构的X2+A710+A510的CPU设计。 我会再专门开一篇专题,在分析高通Snapdragon 8 Gen1 最新的SoC的时候,来看看ARM的公版CPU在具体芯片公司SoC中的落地情况。